Here you can find some detailed informations about the project sometimes about other things I'm working on.

Under the date of the diary entry you can see the theme for the entry.

Most of the ppl fall asleep during read or after ;) it's more or less for me for later readings...

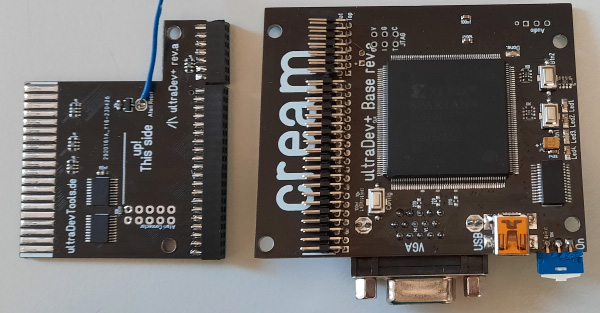

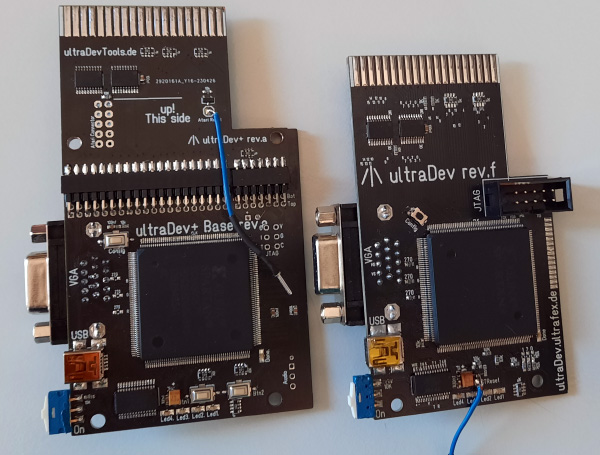

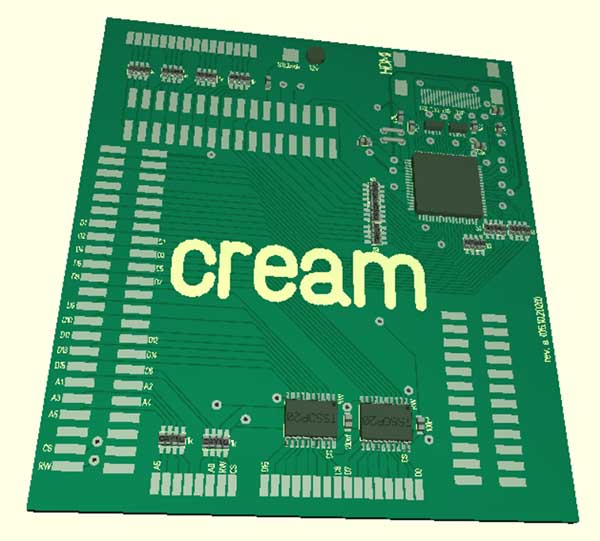

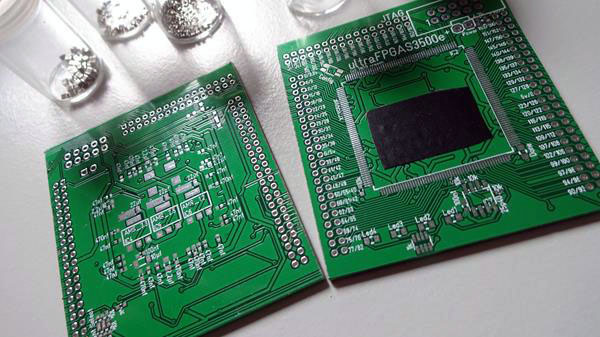

| 06.12.2023 ultraDev+ rev.b |

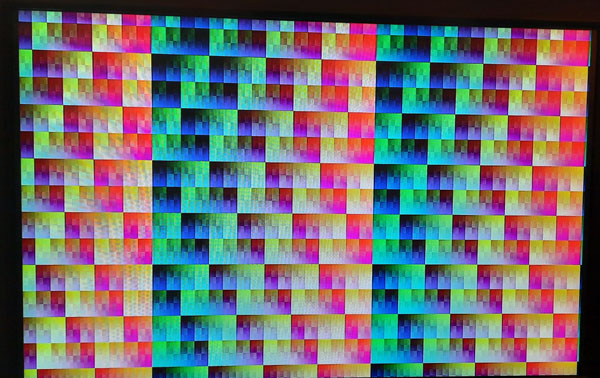

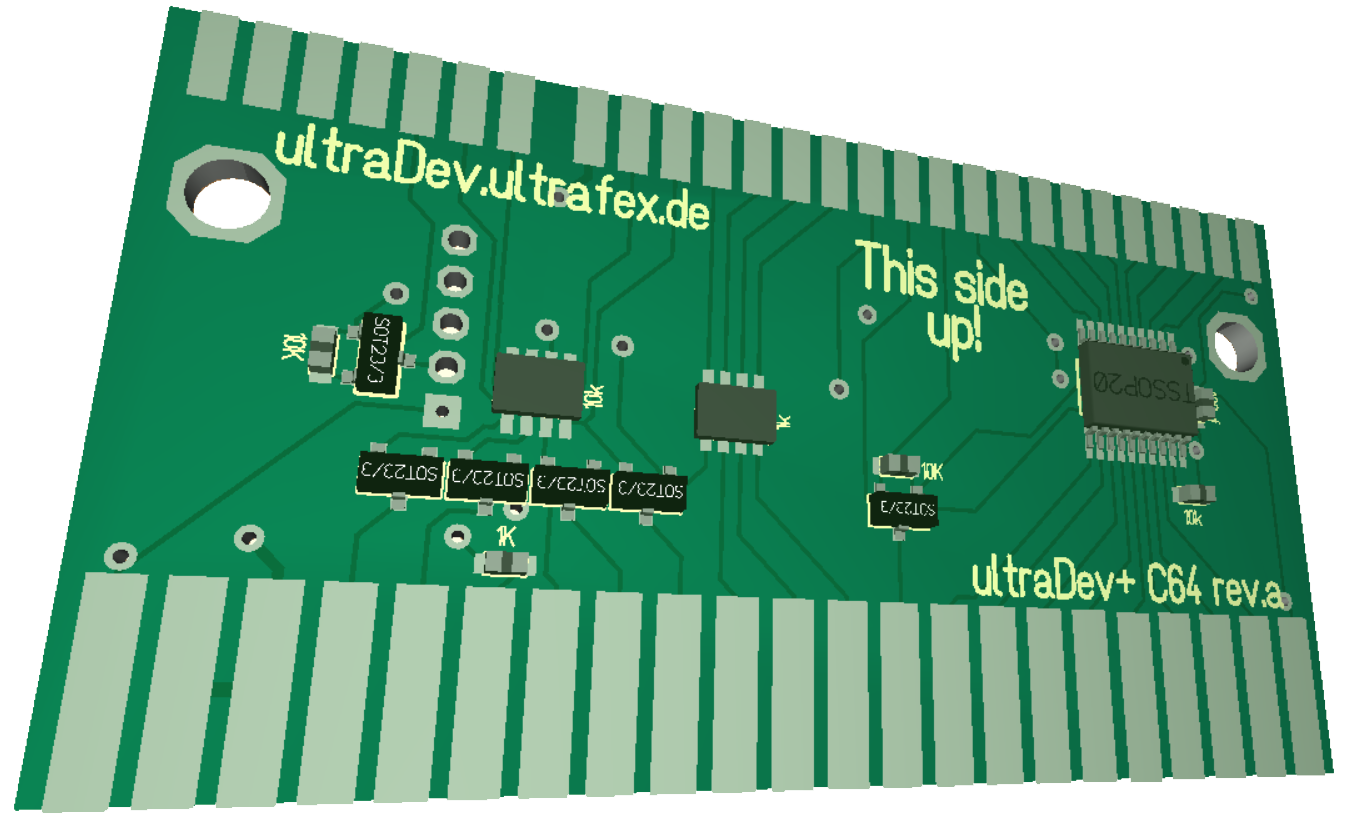

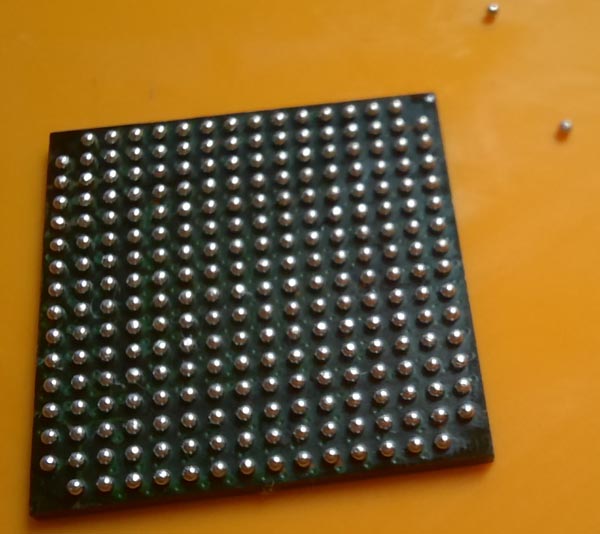

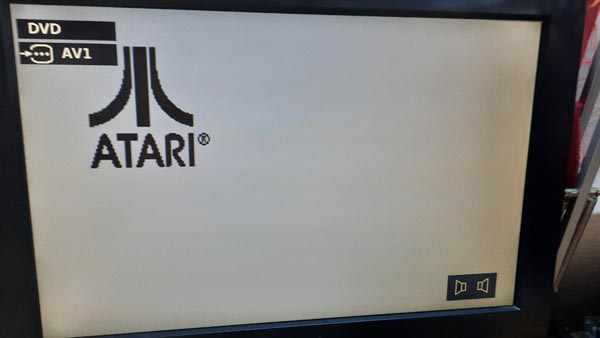

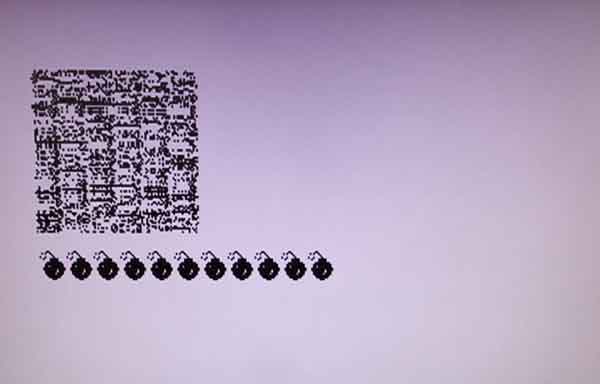

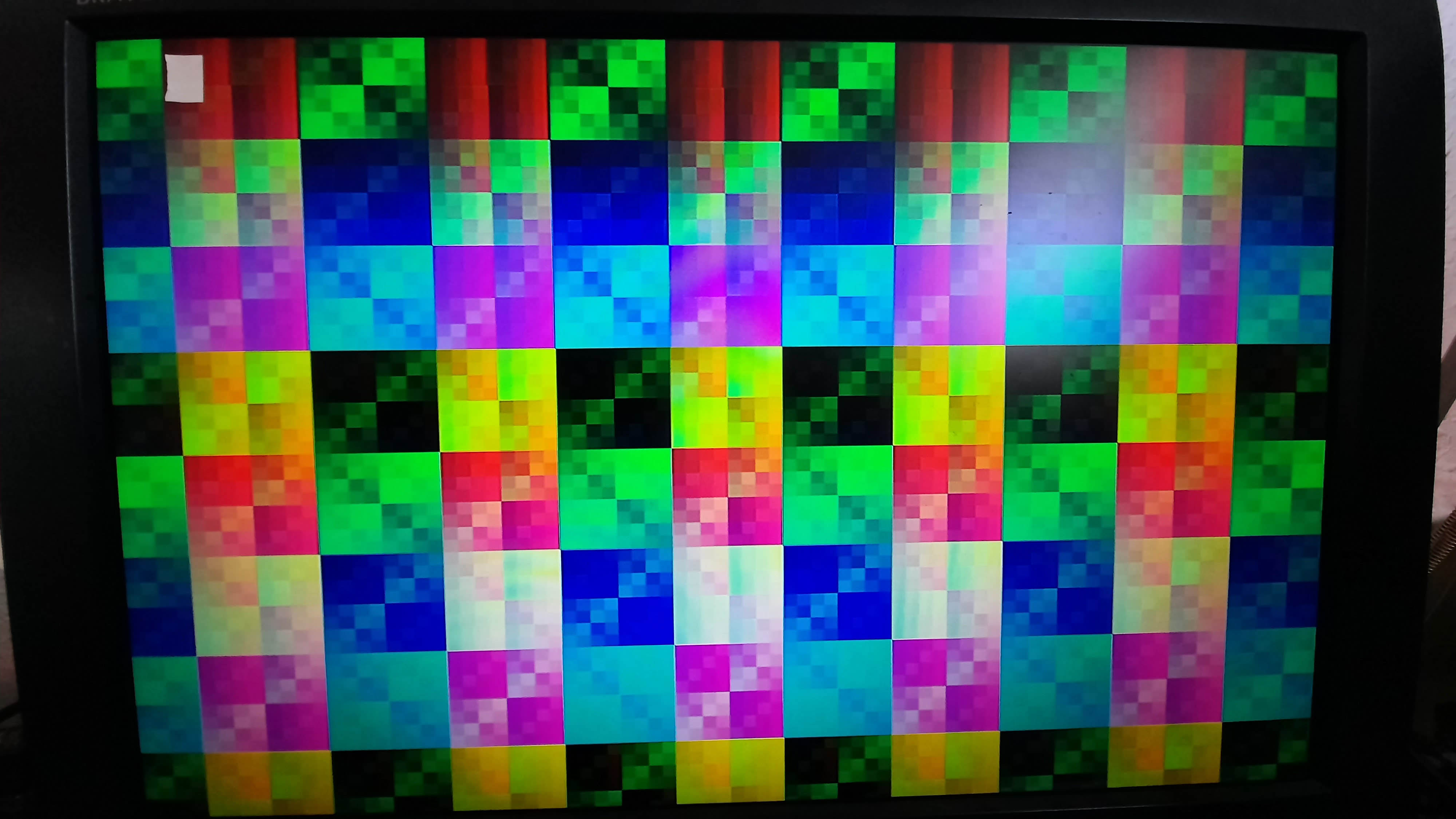

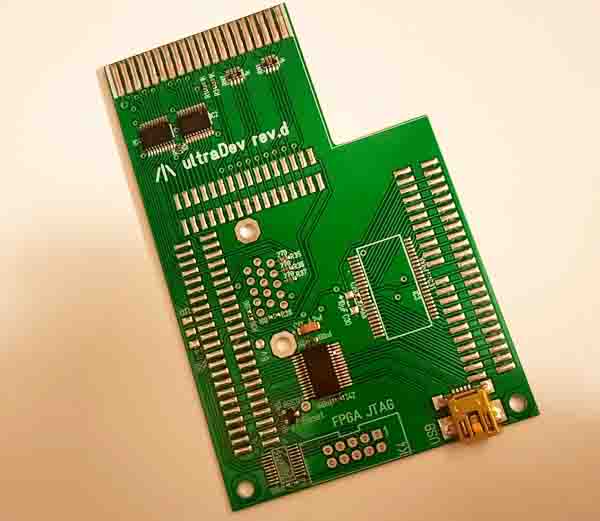

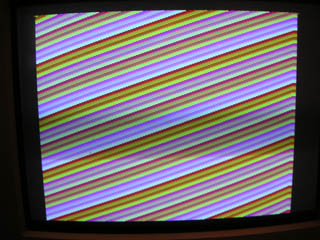

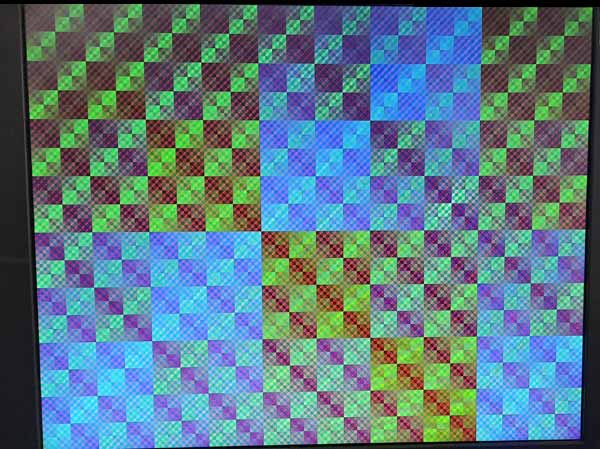

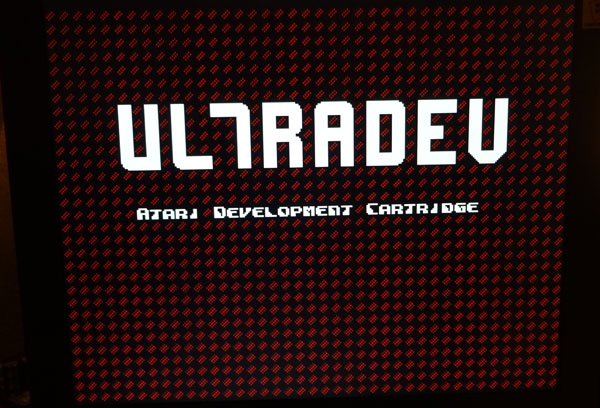

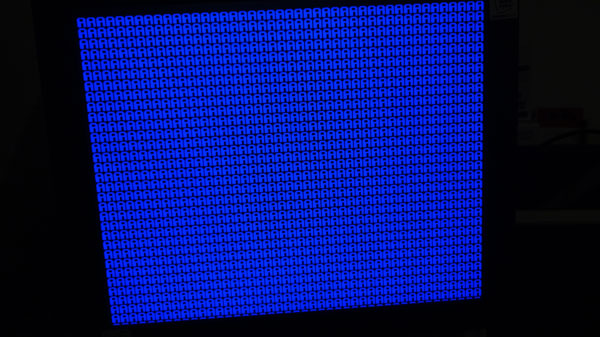

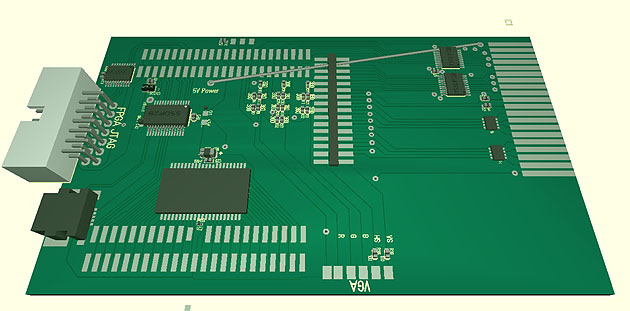

Isn't that beautiful?:

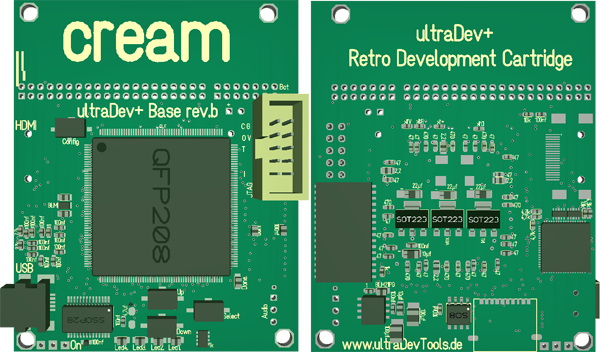

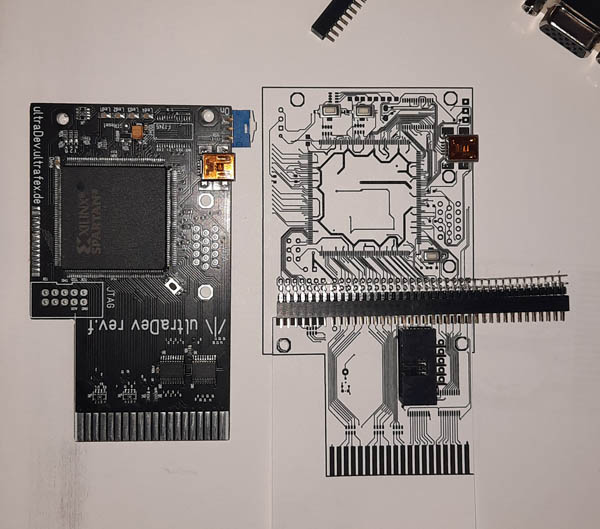

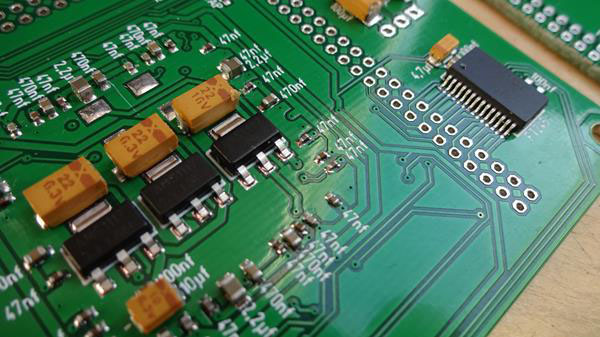

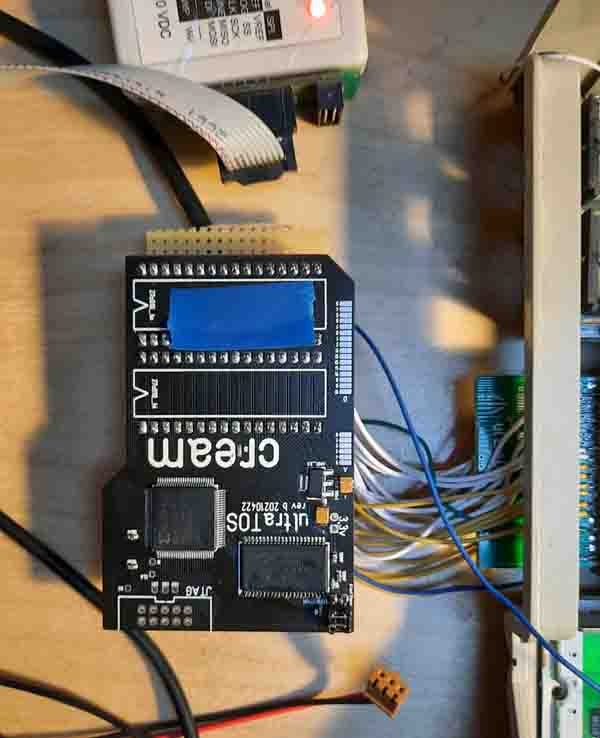

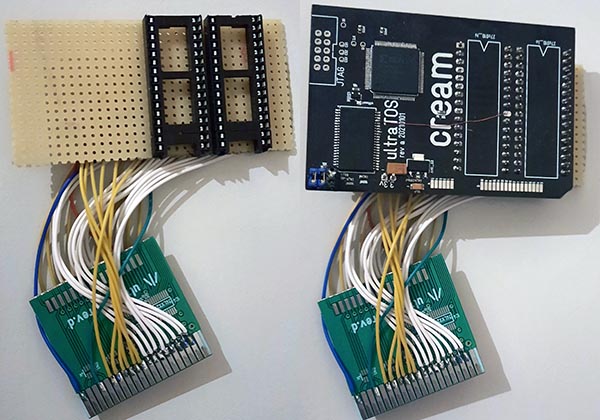

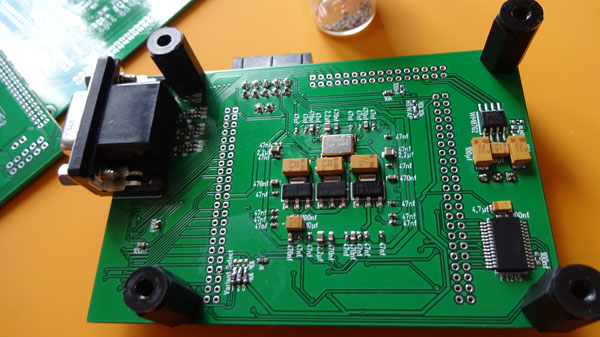

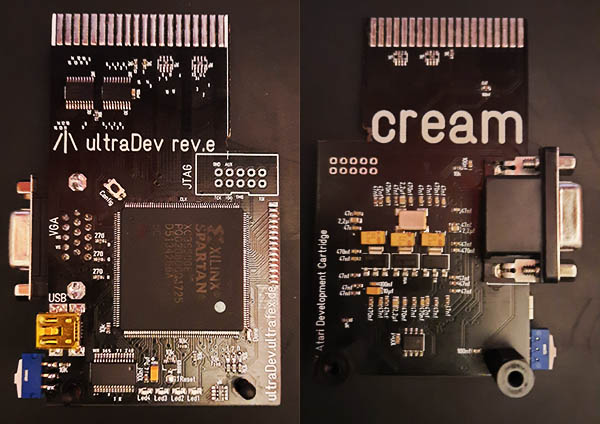

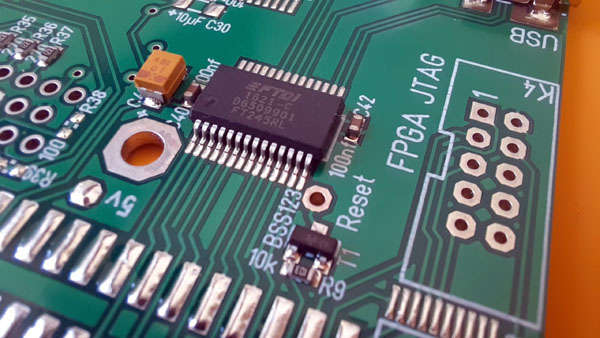

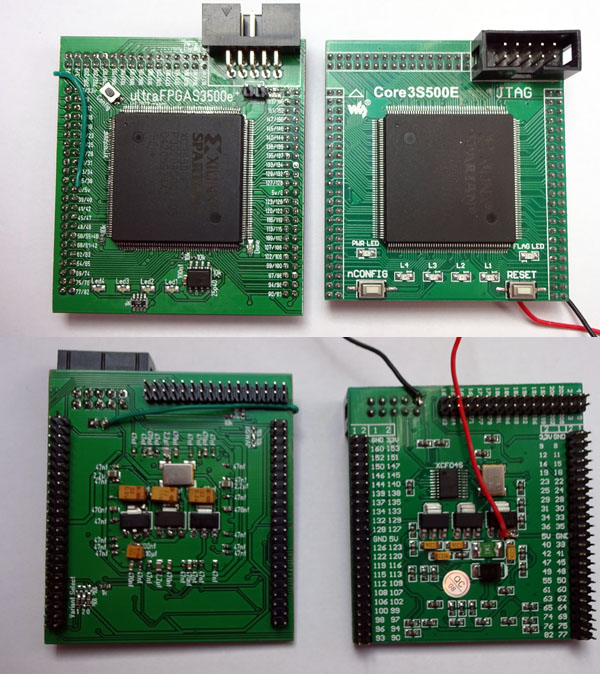

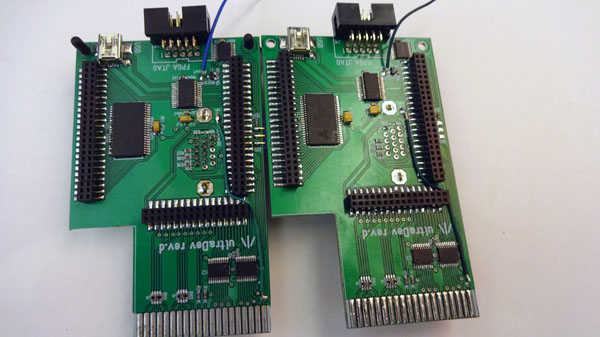

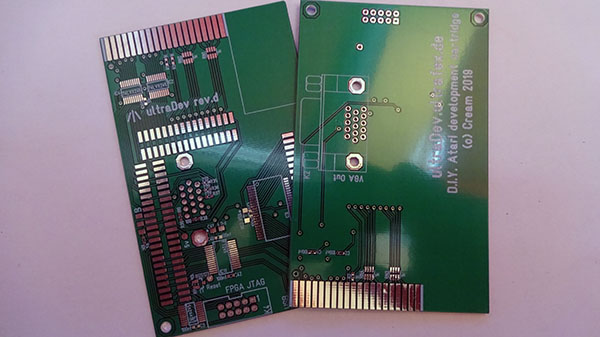

Ok a standard checkboard pattern but this showed me the HDMI output of ultraDev+ is working. That made my day :) The fully built up PCB you can see here on the left (rev.b) on the left the first (rev.a):

As you can see some slight differences on the rev.b PCB on the left side is the new HDMI section. That was a real challenge to layout this on the limited available area. And the upper picture proofs the stuff is working. Cool. The PCB arrived one week ago unforunately because of a cold I wasn't able to build it up earlier. Build up took a while but this is normal. The first build up needs always a bit of time like checking if everything is good to solder and no bigger componets placements mistakes are done. All is fine. Until now I only found some solder mask and text bugs on the PCB but no big deal. So over XMas I have something to play with. I really hope the rest is working fine. HDMI was the most complex new feature which is working fine. That's pretty cool. One week left and my traditinal XMas vacation starts. Nice :) |

| 17.11.2023 ultraDev+ rev.b PCB |

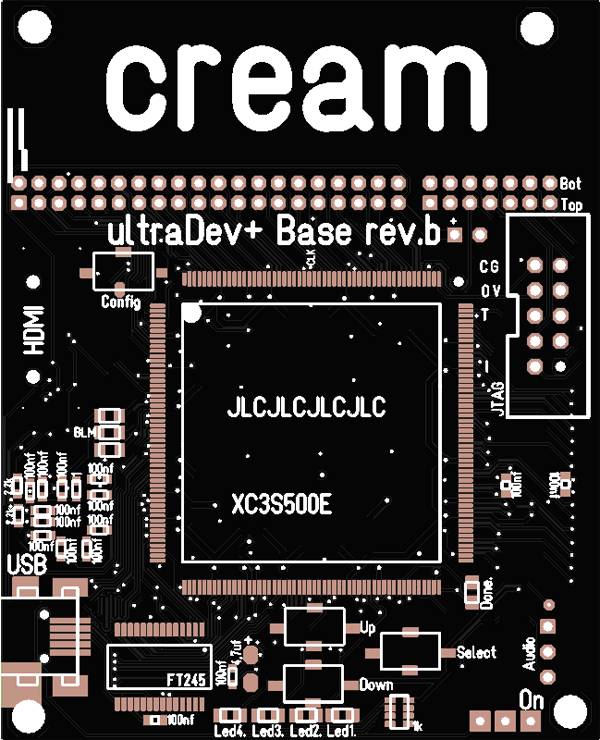

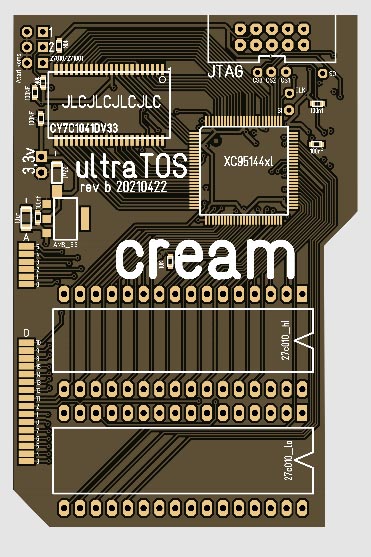

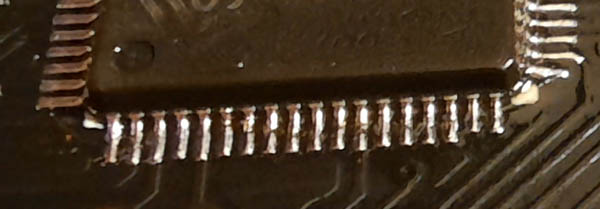

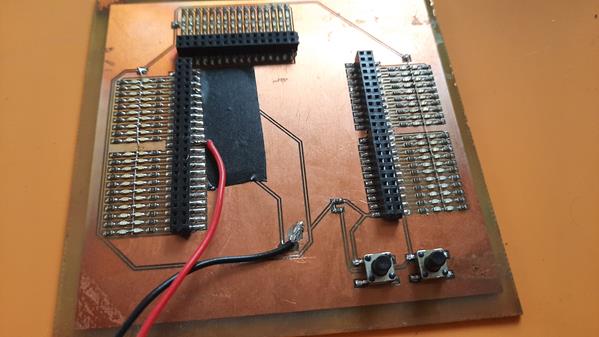

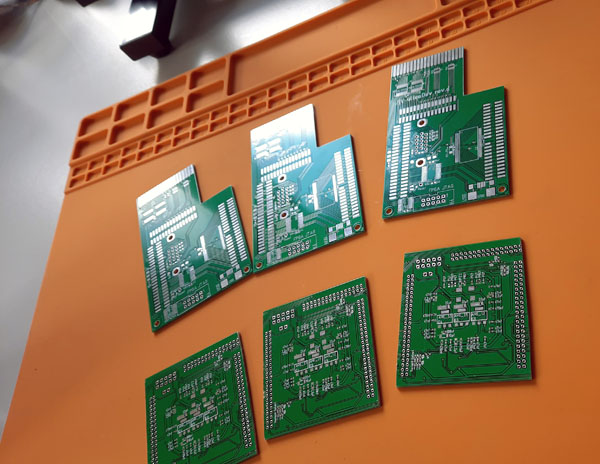

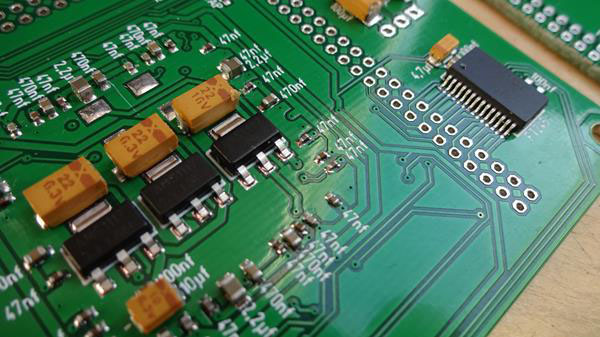

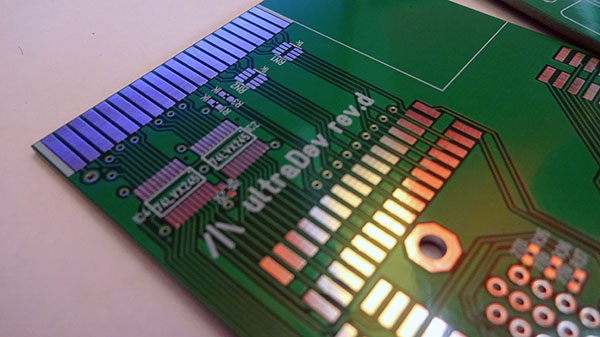

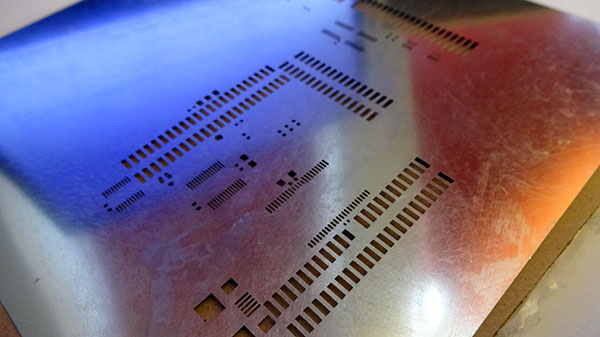

The PCB are done and already send yesterday. Currently the PCBs are in Hong Kong. With some luck they arrive next week. Niceness. I discovered a small bug in the new revision in the layout:

Nothing big just a problem in the solder mask. If you look on the lower left there is too much copper visible. Hm anyway the PCB will still work. Maybe I need to use some black paint anyway... |

| 13.11.2023 ultraDev+ rev.b PCB |

Today I checked the new PCB again and did the last placement test means I print out both sides of the PCB on paper and try

to place the all bigger components. This is a quite important step since you not always see in the layout prg watch a problem is. Today I saw because of the check the sd card holder is too close the on/off switch. Good that I checked this. Next step is to generate the so called gerber files. These files are needed by the PCB manufacturer to produce the PCB. Basically For each layer (upper/lower copper, drills and silkscreen) a file. Next step is to upload the gerber files to the company and pray they accept the files. This time is was quite nervous because all other PCBs I did before I haven't been at the absolut max. capabilities of the PCB manufacturer. Capabilities like minimal track width space or minimal drills for vias. This time I was but it seems they accepted the PCB and they already generating the data for production. Puh... In about 14 days I should have the PCB yay... Time for a project switch ;) |

| 08.11.2023 ultraDev+ rev.b |

Continued the new layout for rev.b and I was able to route the HDMI stuff now after skipping the termination resistors.

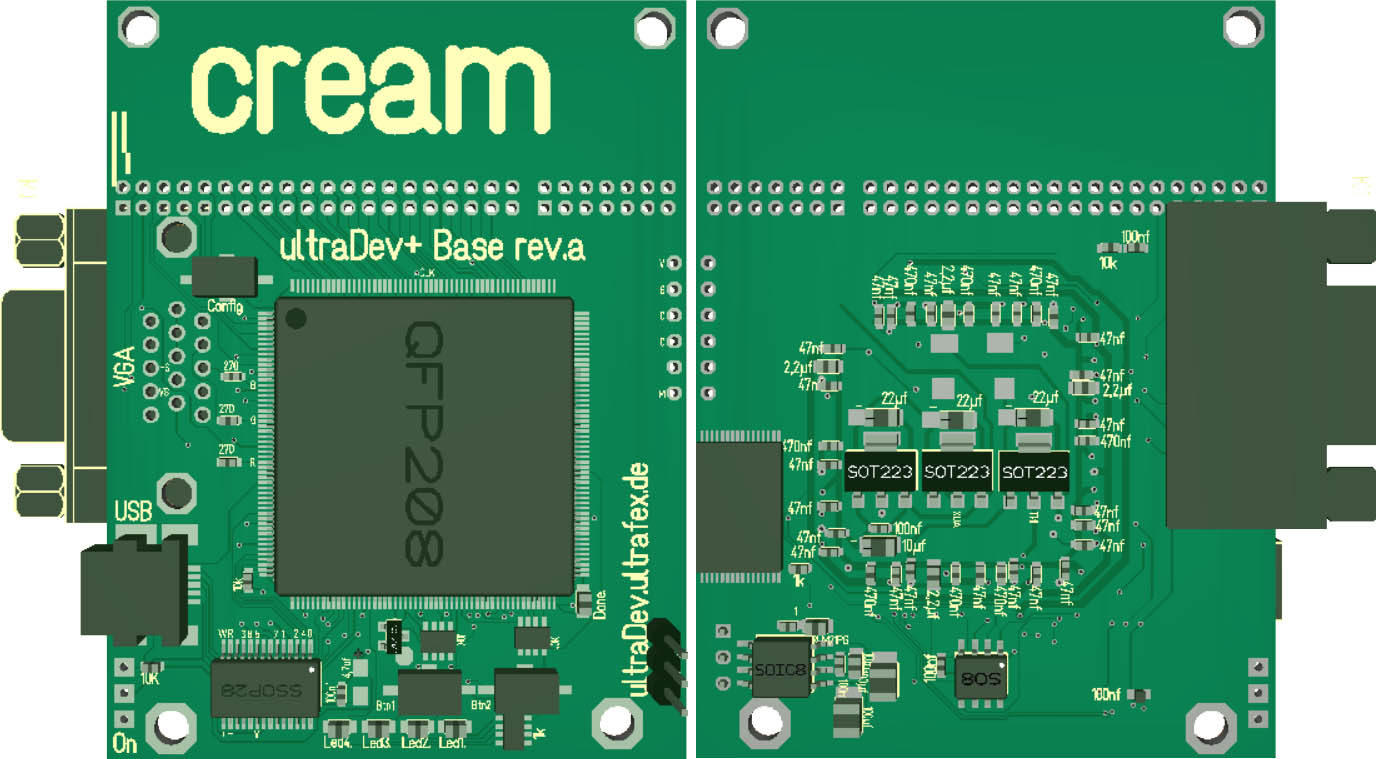

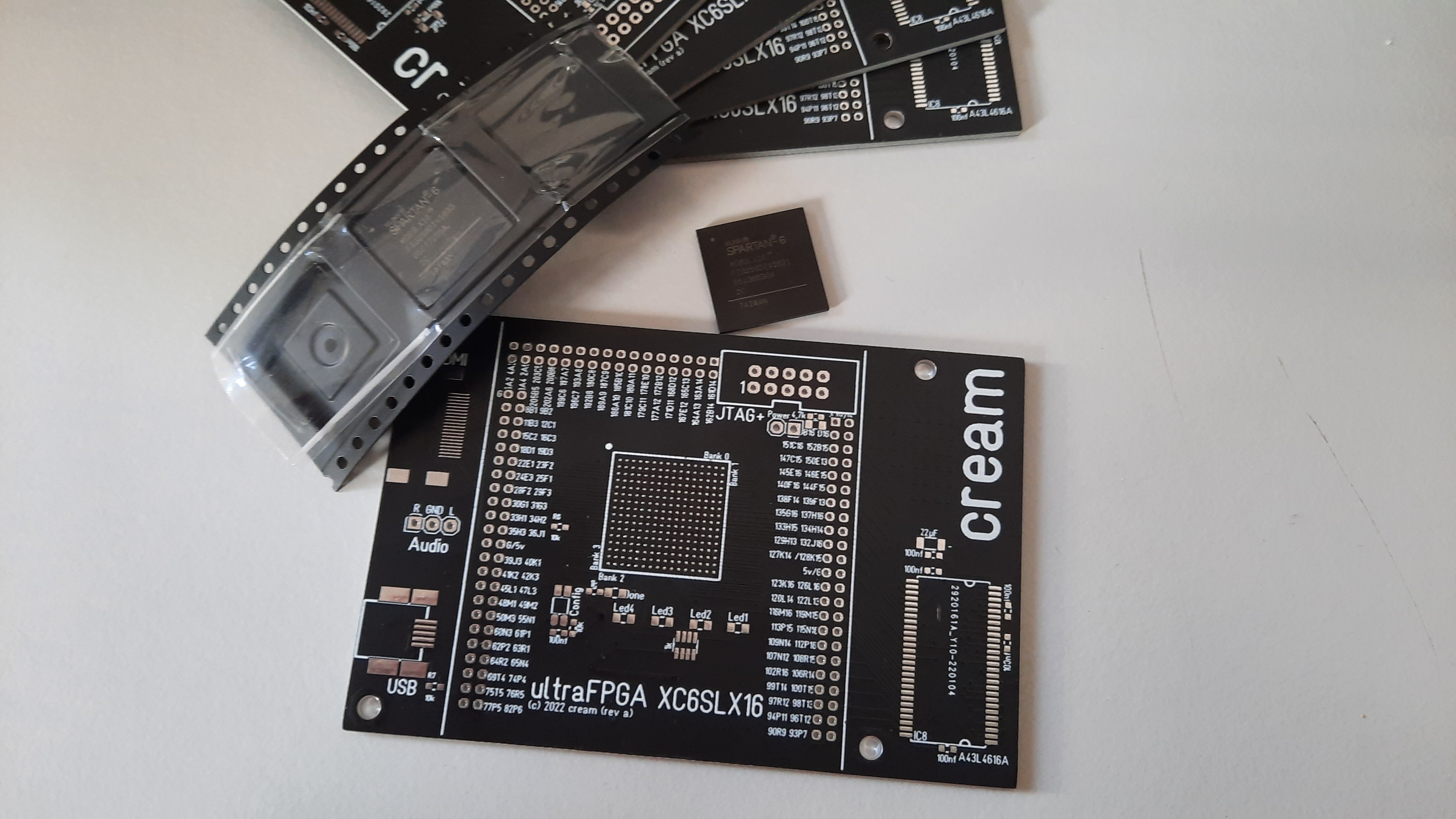

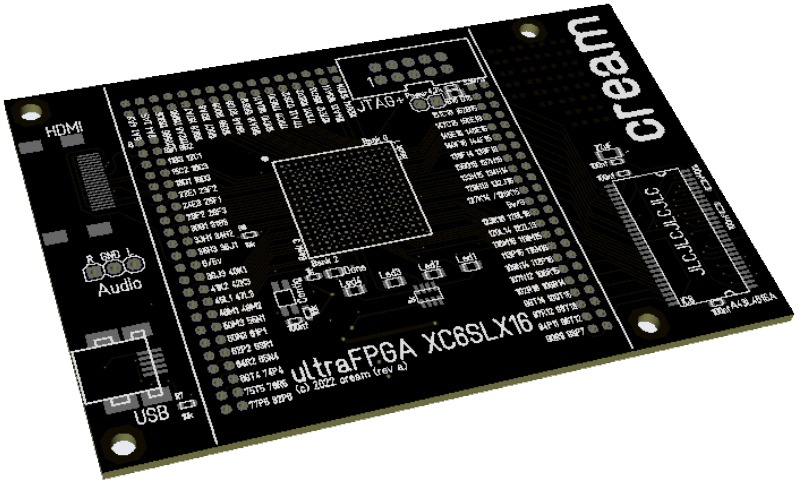

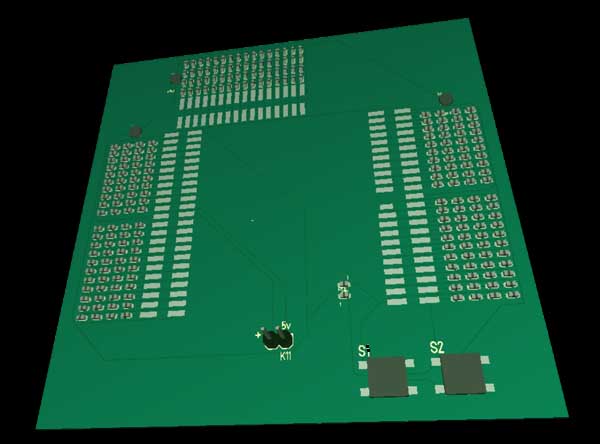

The longest track is about 40mm means the rise time could be about 1.2ns I think this will work. The PCB is not fully checked but my plan is to do this as soon as possible. I want to have the PCBs here over XMas so can work a bit on it ;) This is how it looks like:

As you can see around the HDMI circut (left picture on the left and right picture on the right) there isn't much space to route the tracks. There are about 35 tracks from the FPGA to the HDMI chip. That took ages on a 2 layer PCB to route. So the new stuff is in rev.b:

My new idea would make it possible to share volumes with quite a few gigs. But let's see first the PCB needs to be done... So I hope I can finish the PCB until end of the week. |

| 24.10.2023 Life ultraDev+ HDMI |

Well life catched me again. I exchanged a few heaters in my house. Unforunately this took alot longer than expected.

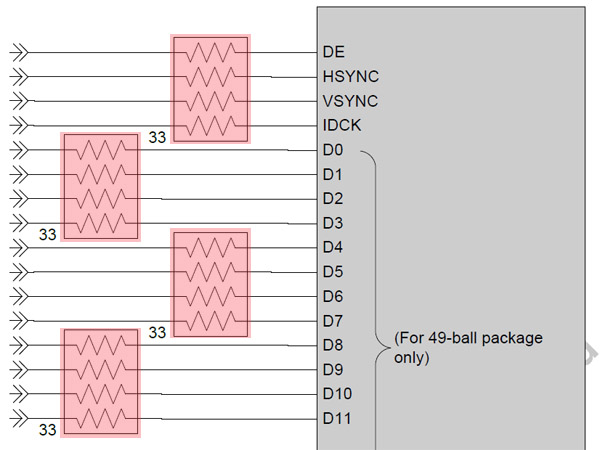

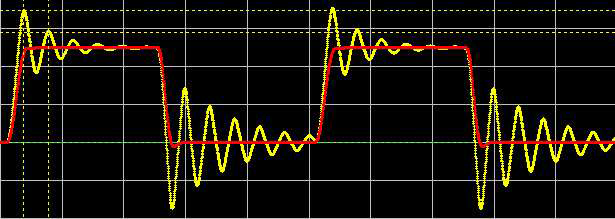

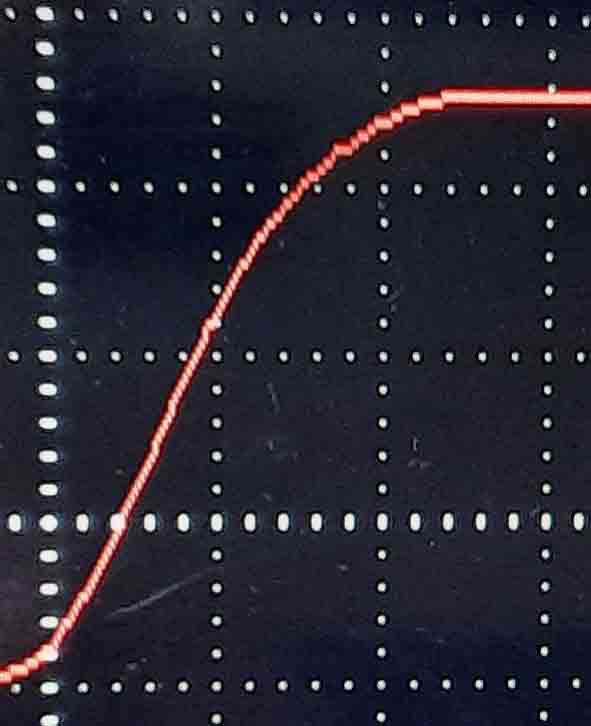

Yeah I could have done this next year but anyway I wanted to have this done before the winter... Anyway. Ah well routing the connections and componets for the new HDMI port isn't easy. There is so limited place and I do not want change to a 4 layer PCB. And even with 4 layers it's almost not possible. Esp. with HDMI you should keep the lines as short as possible. Hm the biggest problem are some resister networks for the lines from the FPGA to the HDMI chip.  As you can see each line needs a resistor. That takes alot of space and I only have about 1,3 cm on the left of the FPGA. In all I need 4 resistor networks with 4 resistors each means 16 x 33 ohm resistors. This is quite alot on this small place At weekend I was thinking mh do I really need these resistors? What happens when I just leave them out 33 ohm for each line sounds odd. How can I proove I do not need them? I'll just note down my thoughts here if I really need these resistors. First of all I did not study electronics maybe my explanations aren't correct. It's just how I understood it. If something is wrong tell me ;) As you maybe know transfering digital signals over a line can be a problem when it gets too long. The result can be a wrong signal at the reiceiver side.  (image is from somewhere on the net forgot from where...) A too long line will create reflections and this is how they look like. You surely can imagine a sensitive receiver of that signal will result in a wrong signal. The resistors in the upper schematics are termination resistors which are trying to reduce these reflections. Alot of ppl are thinking a fast signal causes problems with too long lines but this is wrong. It is not the speed of the transfer it is the rise time of the signal which causes reflections. A line is considered electrically too long when the simple propagation delay of the line is greater than approximately 1/6 of the minimum signal rise time. (from mikrocontroller.net) Propagation speed of electrical signals is 21cm/s. To calculate the maximum length of the line without a termination: 21cm/ns * (1/6*(signal rise time)) ≈ maximal length Ok to calculate I need the rise time of the Spartan 3 port. I measured this with my Osc.  One column in x is about 2ns means maybe the rise time is about 4ns? so: 21cm/ns * (1/6*4)ns ≈ 14cm Even with a rise time of 2ns -> 7cm it would be ok. I think the lines from the FPGA to the HDMI chip will not be >7cm. This is cool. This will reduce the space needed alot. Sure I could have used 0402 resistors and no resistor netzworks but this is a pain in the ass to build up. |

| 09.10.2023 new Project, vacation, ultraDev+ |

Hmm... ok already quite some time passed by... Well at the end of july a new project catched all my focus. Really fun work on

this... But in the middle of august I recognised my batteries are empty and I'm pretty much leeched out. This resulted in nearly

doing nothing for weeks ok to had to work bla just waiting for my vacation. But ! at the end of september my vacation started. Yeah that was good. I have been in denmark for some time and today is my first working day... I'll try to share my time a bit between ultraDev+ and the new project. Ok tbh I'm not very good in this ;) Usually I'm not very good in this. Usually I only can focus on one project and this lasts mostly 3 or 4 monthes and then I need a project switch. Mostly because something different catched my focus ;) But sometimes it's good to have longer breaks. This gives you a different point of view when you change your focus again to the project. Same for ultraDev+. When I started to work again on it mh I asked myself. Why I do not use HDMI? When I started to layout the PCB for it I had longer thoughts about changing to hdmi. 2 things have been against to use it: a) I do not have enough pins. But the HDMI controller I use has a 12 bit mode which needs for the data transfer 12 pins instead of 24. Which I forget. b) I do not have enought memory. To init the HDMI controller I need one block ram which do not have. But now I'm using a 6502 which could init the controller. Hm another thing is. Why I do not have a sd card adapter on board? That could provide a volume on atari with read and write support by default. Without the need of a folder share server running. No question (at least for me folder share is an essential thing) I'll not skip this but having a volume on sd card would be nice. For a sd card I do not need alot new pins on the FPGA. I mean for the boot rom I uses SPI and SPI you can use with sd cards too. So after the break it was clear. I'll do a new revision of the base board of ultraDev+. Well I have some kind of perfectionism. I have to change this.:) And on the other hand it makes no sense to introduce that stuff in a later revision when it's already released and delivered. It makes more sense to introduce this now. Even if it is alot of work esp. routing the HDMI stuff. I have quite alot tracks on very little space. But looks good I think. Most of th tracks are already routed. Changing to a 4 layer PCB is no option. So now I'm really at the max capatilities of the PCB manufacturer. 0.127 tracks and 0.127 space between tracks. Or vias 0.2mm and 0.5 in all. This is awesome. Ok for for 4 layer PCB which I used in ultraBoost it's even smaller... anyway very impressive... So to make a long story short. I'm working a new revision of ultraDev+. I think this is a good step into the right direction. |

| 14.07.2023 ultraDev 6502 CPU |

Unforunately not much time in the last days. But it's working pretty good. The new FPGA 6502 firmware for ultraDev is growing. Uploading of a prg works now. And puh it's not slower than the pure FPGA implementation. Well Since the 6502 is a CPU it of course does not reach the rate of flow like a 100% FPGA implementation. It seems the limiting factor is the Atari. Yeah I guessed this already also you have to take into account the data is read from the cartridge port which slows down the access. I think hm didn't measured this yet I'll do the next days... So far Uploading of a prg, 6502 firmware, 68000k firmware is working. Currently I'm working on the volume share. If course it's a bit of work but the flexibility is awesome also it's absolutly fun to work on this. It's like creating a computer in hardware. This must have been the same feeling when the creators of the Atari or Amige have been working on the computers. Sure it's more challenging doing this is real hardware I ment more what do we need? How can we do it with the stuff we have? Or do we need another chip? For example I recognised it would be really nice to a have some kind of timer in the 6502 maybe to create a task which should executed in an interval like a blinking led or a time out. So I'll just include some kind of a timers maybe 3 or so which can create irqs. That's fun the flexibility of FPGA is so brainblasting. Normally I planned to do more CPU based hardware things. But somehow FPGA I can't stop working with them... Also with ultraDev have the perfect application example how to use the FPGA. Often ppl do not know what to do with the FPGA because they do not have an application what to use it for. Theoretically you could add new FPGA commands for this I'll add to the ultraDev.exe the possibility to send custom commands. What the command does you can decide in the 6502 firmware of the FPGA. Also I'll add a possibility to upload/execute 6502 code from the Atari. Means you would have a second CPU running with 50mhz. Very like the host interface to the Dsp on Falcon. Of course a 6502 will "never" reach the speed of the DSP even with a fast 6502. But an advantage is of course the host interface would be only needed to transfer the 6502 code. Accessing a calculated result of the 6502 could be done directly in the cartridge space since the 68k has direct access to the 6502 space. I like the idea ;) Sure most of the ppl will not use this... |

| 07.07.2023 ultraDev 6502 CPU |

Oh man. The last week have been really terrible. Basically the 6502 memory Interface worked

but by adding more features to the interface it ran into more and more problems. Also multiple writes from the 6502 core have been a problem. Well normally I do almost 100% synchronous code almost everything I did is synchronous logic. For the memory I had to use combinational logic. Of course some standard things you need to use combinational logic like creating a port on the fpga which can be an input or output like the ram data ports. But... What is the difference between synchronous logic and combinational logic? Synchronous logic is synchronous to the clock means the values can change only when clock changes (posedge or negedge). Also changes from the inputs are only recognised when the clock appears. Combinational logic the inputs are evaluated "immediately" same for the outputs. Means the reaction time is alot faster then the synchronous logic... Of course you can do most of the stuff with synchronous logic. In case of the memory interface it was no option to use synchronous logic. When the 6502 for example reads from memory it gives the address to read from and expects the result on the next cycle. When you use synchronous logic here you will have a delay till you have a result because the synchronous logic will see the read too late and when the 6502 excepts the read data is not available. Anyway but realising this needed a few recoding of the memory interface since I never did this until now. And showed my ignorance for this topic. It was a real pain in the ass to do this tbh but I learnt alot. Also showed that the Xilinx tools esp. the simulator is an absoulte piece of shit. I was working the entire week with that thing and had 100 or 150 crashes? Holy shit that was so annyoing... Was not easy to manage this. Quite a few times I switched off the computer and thought fuck you Xilinx. Anyway it's working now I really hope it stays like this. |

| 30.06.2023 ultraDev 6502 CPU |

Uploading of the 6502 works now. Wow what a development time improvment...Just assemble and I can change the behavior of the FPGA.

Now I'm working on some standard routines printf style text printing with hex values in a string for debugging.

Also I started to code the upload for prg files but not finished yet. It was more important to have some nice debugging basic routines. A real journey I had with the assembler this week. As I wrote before I've decided for acme. But somehow this assembler is really retarded. Macros are a pain in the ass and I was not able to do what I wanted to do. Guess ;) Yeah I kicked acme now and tried Kick assembler again...Changed almost the entire sources to Kick assembler and I don't know like it. So I skipped Kick assembler again. And in the end I'm now using dasm again. Somehow I like this one most. And besides there is a nice vscode extension with some more advanced features for dasm...Nice.. Somehow it feels like comming home...;) |

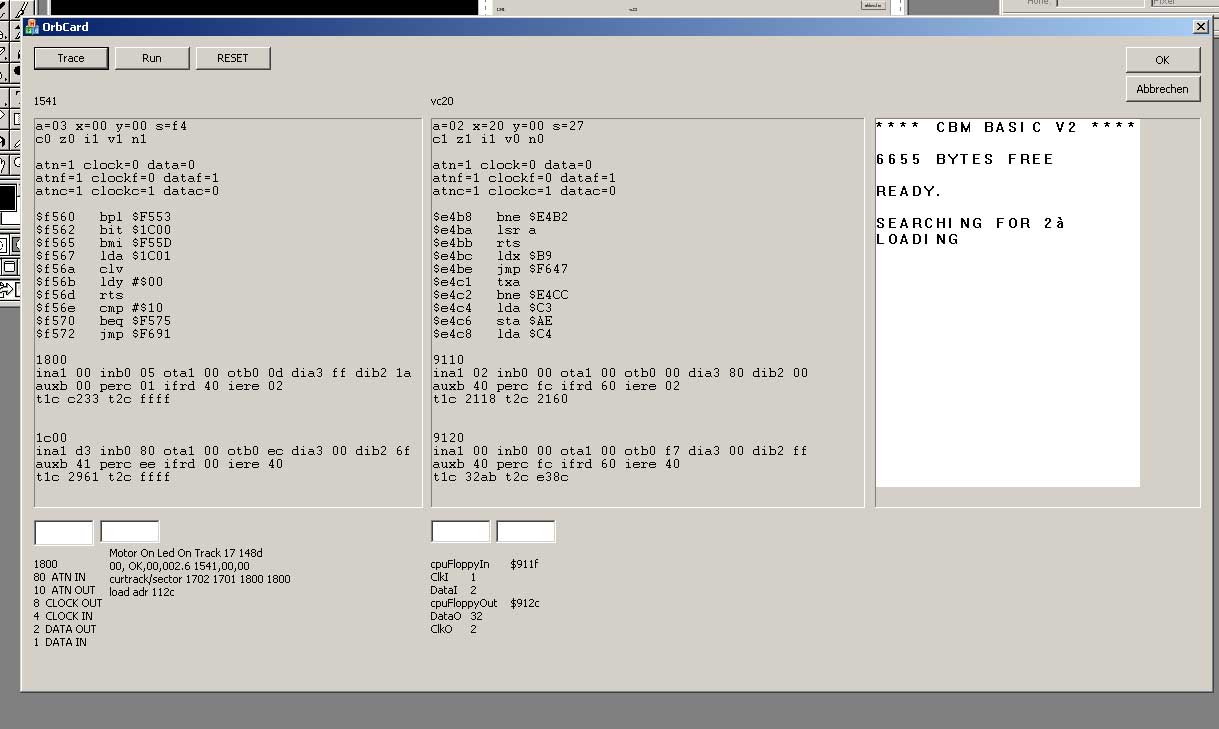

| 24.06.2023 ultraDev 6502 CPU |

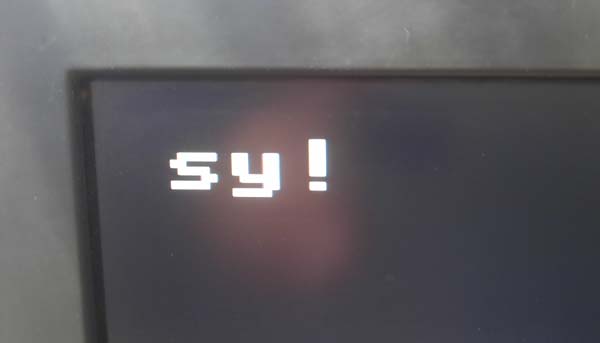

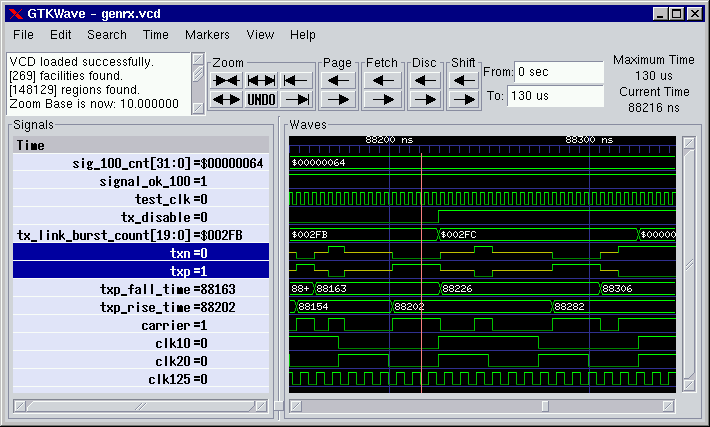

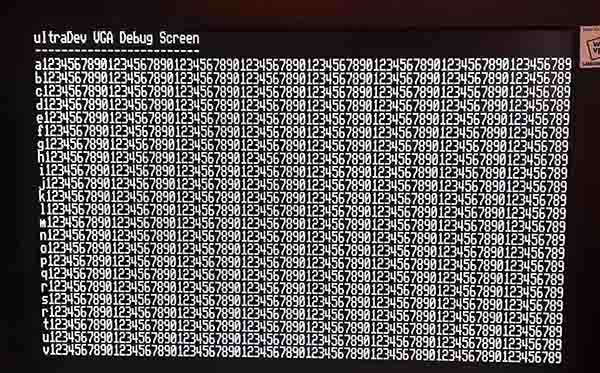

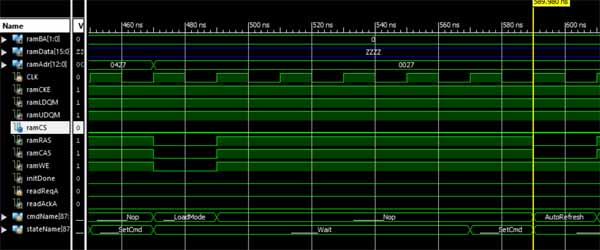

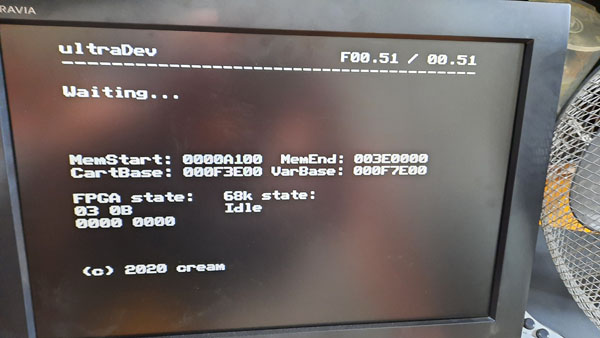

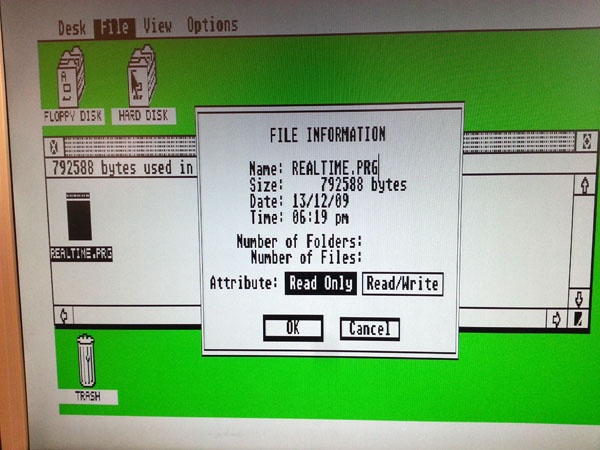

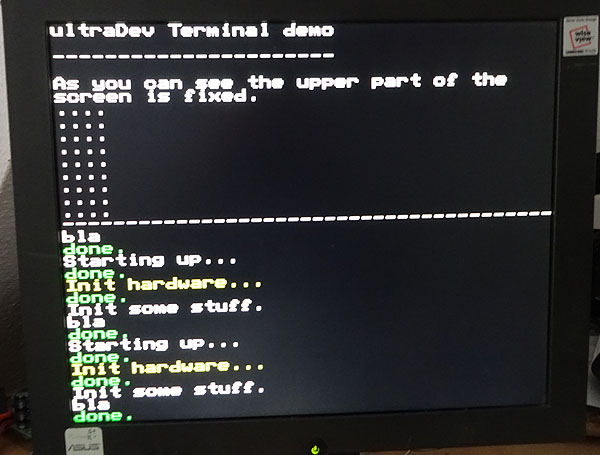

That made my day ;):

This is the first working USB communication with the 6502 core. Yeah as you can see the 6502 can write to the screen too. That's very nice for debugging. The communication between host and FPGA is command based means SY is the sync word directly followed by the command id. Since the debug screen the font starts ascii code $20 S becomes an s and Y becomes y.! is the command id means 1...1 is a Get FPGA version. The 6502 code for the answer looks like this: cmdGetVersion: lda #$12 +USBWrite lda #$34 +USBWrite rts And the version $1234 I get in the ultraDev.exe. Puh that's pretty cool. It's so easy now to add new commands to the FPGA behavoir. Normally you need to define states in the FPGA state machine, do the code, test that's so much faster to develop... Basically I have all I need to code the first more complex commands. Of course upload of the 6502 code is the first I'll do. Nice! |

| 20.06.2023 ultraDev 6502 CPU |

Ui it quite "hot" in the last day here in Germany. I'm happy I isulated my roof and walls so it's not getting too hot here in my working room. But still too hot somehow to do accessive coding But still today we have around 30°C I really hope it's getting better soon... In the last day I continued working on the 6502 and FPGA memory interface. Coded a new USB communication module for sending and reading a byte over the FT245 chip. And well after finishing it was time to select a 6502 assembler. Hm after asking axis which should I use? Well seems there are several assemblers out there which are used. Hm I tried out kick assembler some time ago so far I remember somehow I didn't like it. Dunno what is was. Of course I used 6502 assemblers before. The OMD (VC-20 demo) or No Pets Allowed (Pet 4032) have been done with dasm. But I think dasm is not really standard. So to make a long decision story short... I decided to use acme. So after starting the 6502 code for ultraDev I had to change the entire project and top source. Ui quite a bit of changes. And what do you do I you try out something new? mh? Yeah let some leds blink. (You can see at the lower side). I know doing a video with blinking leds is well not very impressive... But this was a small success... Somehow I love linking leds. That must be something from my childhood or so dunno. My partens always had a good present if the it had some blinking leds in any way...hm anyway;) So the 6502 CPU inside ultraDev is working. That's pretty cool... But somehow I wasn't able let the 6502 CPU run at 100MHZ hm somehow the logic is too slow. It seems I had a misread when I selected the 6502 CPU core. It runs at 100MHZ on a Spartan 6 I'm using a Spartan 3 Hm running at 50Mhz seems to work. I think 50mhz is still fast enough. Sounds not like a problem to use 50mhz. But different clock domains inside a FPGA is more work. I mean using memory or writing to flipflops from one clock is easier. Really hope this will not be a problem did do this too often. But it's more work to get this working. So currently I have 50MHZ, 100MHZ and 108MHZ but there will me at least one more. So it really exciting currently. I think I really can start soon with the basic stuff like uploading a prg. But really alot of work since I have to recode most of the FPGA code in 6502. But for sure this will be alot faster (coding time). Tbh I didn't expect the led blinking would work on the first try. Simulating your stuff rules and saves time ;) Coding on FPGA is as I said quite often quite different. On a CPU you do not have to fight with all these stuff. So really the next what I need to get to work is to make it possible to update the 6502 code from PC. If this is working it will be awesome. I do not need to create the FPGA programming files each time. I just can assemble and upload. This is a question of seconds instead of 3/4 minutes and even more if you simulate the stuff before... Just Awesome! ;) |

| 17.06.2023 Kieler Week Bus interface 6502 CPU Website hack |

Yesterday the world biggest sailing even started in my home town. The Kieler week. Really alot ppl are comming over during the week and the entire city is

full of ppl. Usually it's not downtown is more or less dead inside the week. So finally something up here.

Kieler week is so far I remember 10 days long.

With over 20 stages in the entire city with free concerts it became a mega party even in the last 20/30 years.

Kieler week is so far I remember 10 days long.

With over 20 stages in the entire city with free concerts it became a mega party even in the last 20/30 years.That's really fun I've have been there yesterday and well I had the impression yesterday that people have to catch up on something after the corona years. unbelievable many ppl have been there.  Even some bigger bands are comming to the Kieler week. So I guess that will leech some time the next week. Stupidly, I'm not on vacation... anyway

Even some bigger bands are comming to the Kieler week. So I guess that will leech some time the next week. Stupidly, I'm not on vacation... anyway The week ends with the traditional firework.

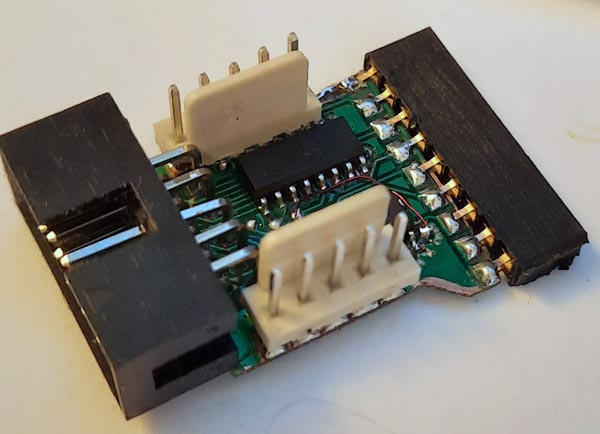

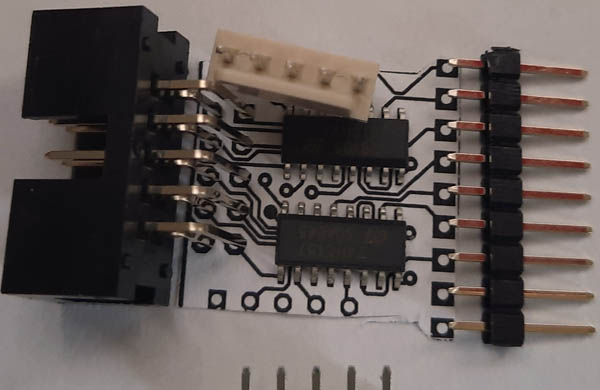

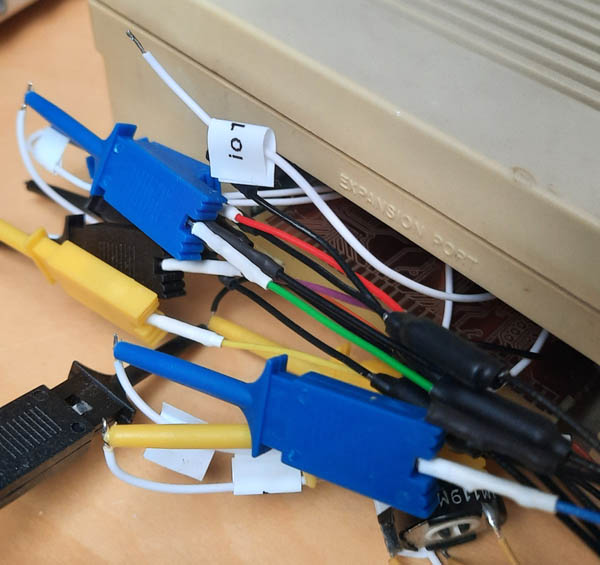

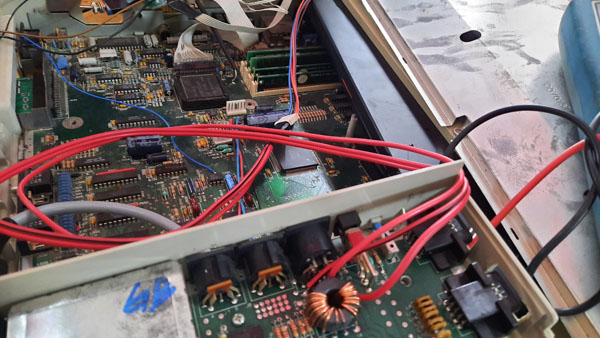

The week ends with the traditional firework.The atmosphere is absolutely awesome. And everyone is sad the week is over. Ok some of them are certainly happy it's over ;) Because going to the Kieler week every day and then to the clubs until the morning is really exhausting. I did that 20 years ago but well I'm too old for that...;) Tbh I have been a bit lazy to update the site but I haven't been lazy ;) During my vacation I finished the bus interface but mh  Somehow I'm not satisfied it's fiddly to build. And the bus interface is difficult to unplug. I think I' redesign the PCB again (that is already the 3. version then)

But I think this is better...

Somehow I'm not satisfied it's fiddly to build. And the bus interface is difficult to unplug. I think I' redesign the PCB again (that is already the 3. version then)

But I think this is better...Currently I started to refactor the entire FPGA firmware. Well as I mentioned earlier I'm planning to add a 6502 CPU to do the entire USB communication between FPGA and host computer. That will be a bit of work but it's worth to do this. This also gives others to change the FPGA behavior a bit. Sure the interface to ST will not be done with that. The 6502 CPU will also have access to the debug screen which will increase the development time alot. I mean changing something in the FPGA code costs round about 3 minutes to implement the design to a file which I can upload to the FPGA. For more complex things you usually need to code test to simulate the new feature. FPGAs are parallel processing and it's not always so easy to code new stuff without tests. Currently I'm working of the bus interface between the FPGA and the 6502. Luckily the everything fits into the memory of the 6502: $0000-$0200 Mirrowed from $e000 $1000-$2000 Hardware registers $1000-$3000 Debug screen $4000-$7fff 68k firmware memory $8000-$bfff Data memory (hd buffer or send data to atari) $e000-$e0ff Zero page mirror $e100-$e200 Stack mirror $e200-$e290 Jump table to communication routines and usb routines -$ffff 6502 fpga firmware memory As you can see the 6502 has access to the 68k code/data and as mentioned before to the debug screen. Of course it's possile to upload the 6502 code during run time. This is really what I love about FPGAs its flexibility you can create interfaces or if you need a different screen output format on vga for example you just do it. It's really comparable with Lego. I loved Lego back in my childhold because of its flexibility. So mainly I'm doing some test fixures to test the interface. But currently no implement for the FPGA I did. I really hope the interface and 6502 is fast enough to run at 100mhz. But creating the 6502 firmware later will be surely alot of fun. Really cool is its flexibility. Finally my www.ultrafex.de site is back. Have been hacked and I remove the inserted code. Seems it was originally planned to grab credit card infos from back accounts. I still don't know how they did this. Anyway changed all passwords now I hope it's not happening again... |

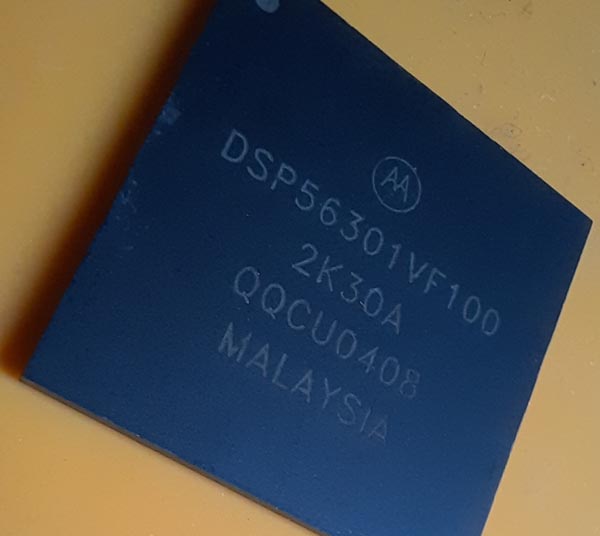

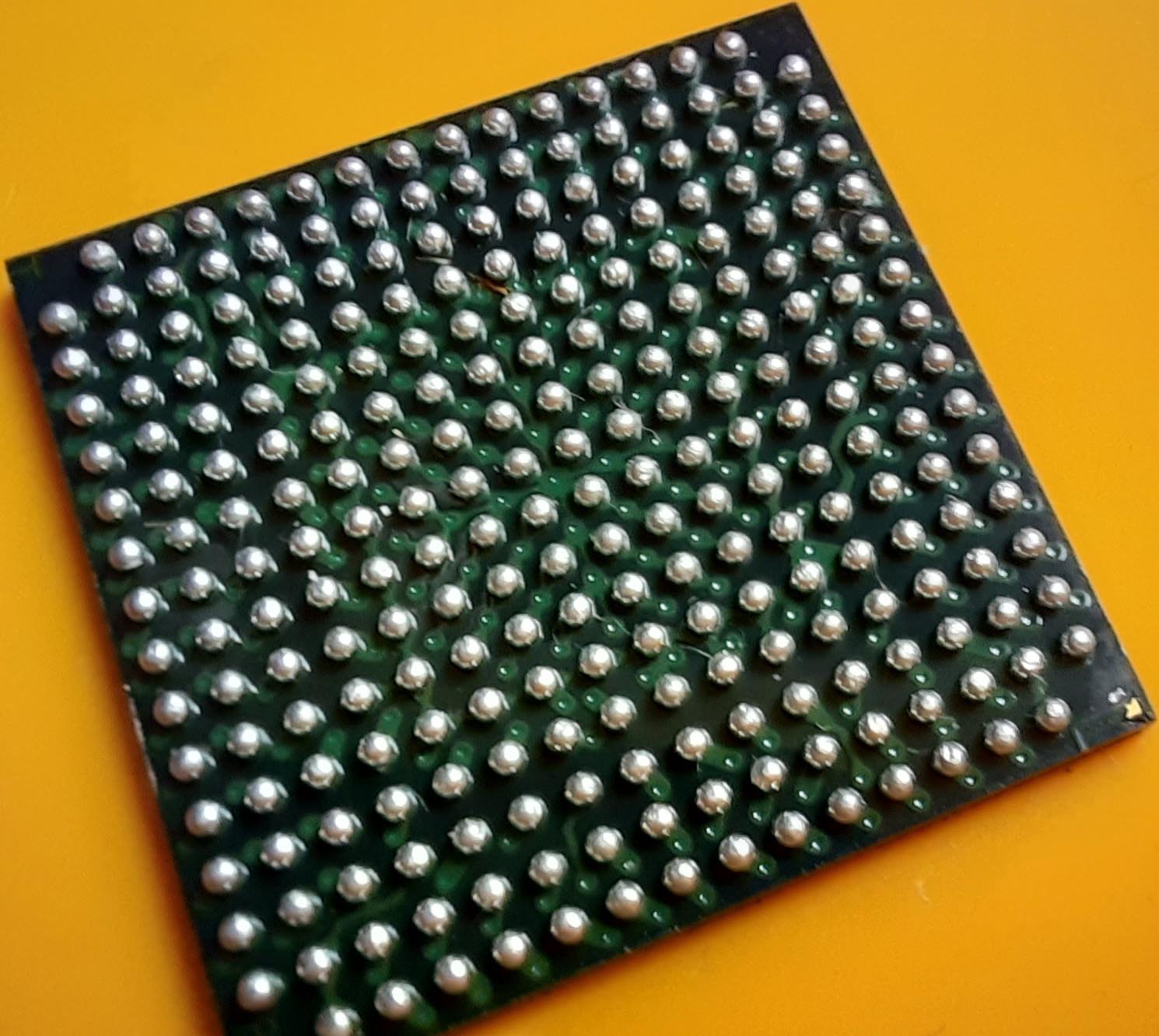

| 03.06.2023 Vacation ultraDev+ STE FPGA code Website hack |

My vacation was pretty nice and relaxing. This time we have been in the south of Germany. Well Usually we travel a bit further

for vacation. But I have so save a bit of money for the house... anyway But south of Germany is nice.  As you can see quite some mountains. We biked alot but well this day we go there by using a cable car. We had to go to the cable car station

up to 400m and this was already quite exhausting. I'm too old for that ;)

As you can see quite some mountains. We biked alot but well this day we go there by using a cable car. We had to go to the cable car station

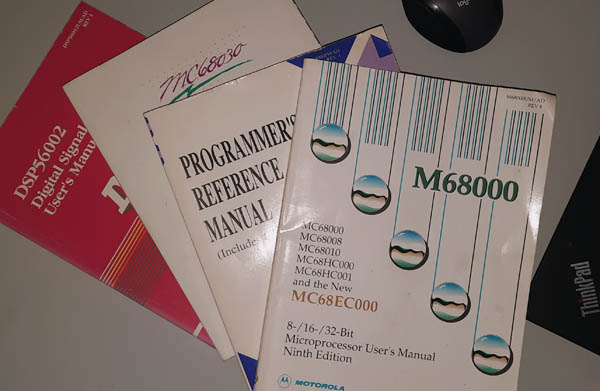

up to 400m and this was already quite exhausting. I'm too old for that ;)We had 2 weeks of sunshine friendly ppl and well food in the south is nice too. Of course alot of time during biking to think about the future of ultraDev and where I want to go with ultraDev+? Our travel we did by train. So I had alot of time to read stuff... So what to read?  Yeah excatly... finnally I read the User's Manual for the 68000. Really interesting reading esp. when you are about to do some 68k

memory stuff.

Yeah excatly... finnally I read the User's Manual for the 68000. Really interesting reading esp. when you are about to do some 68k

memory stuff.Hm as I mentioned earlier I should have read that before I started to develop ultraDev+ but luckily reading it had not direct consequences to the hardware design I did for ultraDev+. Also I finally know how the Atari or better the MFP generates its interrupts. I mean when I coded on Amiga and ST I knew the 68000 has 7 interrupt levels which are initiated with the 3 pins IPL0-2. The Amiga and Atari has its well known auto vectors starting at $64 for each level. But how does this works for MFP irqs? I mean requesting a normal irq you just pull down the IPL lines and the 68k starts an irq. But all the MFP irq are starting at $100 the user irqs. How does this work? This depends on if the avec (auto vector) signal is pulled down or not. If pulled down the 68k uses the auto vector vectors for the irq. If not pulled down the 68k initiates an irq acknowledge sequence and waiting for the vector which should be called from the user irqs. The initiator gives during an irq acknowledge the number of the vector on the bus. Interesting. I didn't know. Doing this here is mostly investigation since I'm not very into 68k hardware. But interesting for sure! As you can see quite some other books for the 680x0 and DSP. When I started again to code on Atari back in 1999 I ordered these book from Motorola for free. For free from US that was quite cool. Mainly I was interested in the 68000/68030 Programmer's reference. Why not to order the other 68k related stuff...TBH I never thought I would have a closer look in 1999 to the User's Manual since it's hardware related only. Good that I ordered it... Just 24 years later I read it fully ;) That Motorola service was nice. Later I ordered some samples for DSPs:  Not sure if NXP still offers this service... anyway During biking had alot of thoughts about if the planned lines for the bus interface is really enough. Is it enought to create all what I want do it? My orignally planned interface has 10 lines. Hm... Did I ever mention I have some kind of perfectionism? So the answer is clearly no. 10 Lines aren't enough. Originally planned all addresslines and the read and write signal. After a long process I decided to change the bus interface means I'll still use 10 lines which go inside but I'll add a small pcb inside of the STE to grab more signals. Today I started to create the PCB. That's the small pcb:  It still receives the 10 lines from the ultraDev+ PCB but by using a multiplexer I can grab 16 signals from the STE. Yeah alot more. But still not perfect. Basically it would be possible to access the memory from the STE by DMA. Means it would be possible to debug directly on pc the memory content. Even if I would have loved to included that I decided it's too much work. The gain what you get is too less... Really hard to decide this. Would be cool but I guess no one needs... That would have mean to recreate the Atari 16bit interface by using a CPLD (small FPGA brother) But is it really needed? No. That was a hard decision but it's not worth the work. The small PCB where I planned to add it. Also I need to consider it must be a) as easy as possible to build up b) as easy as possible to install.  Space is a bit limited but hopefully that will fit. With this interface I'll be able to grab following signals: a23-16 dtack address strobe 8mhz clock display enable horizontal sync vertical sync read/write signal Thats already pretty much what you can do with these signals... So after the planning for the bus interface was completed, I thought about how to proceed with the FPGA firmware. Well that was my first bigger FPGA code and with a view to supporting even more platforms. What does that mean? Is the current good design enough to do that? Is it flexible enough? I do not think so... The code is oki and I'm fine with it. The entire communication between the host computer and FPGA is done in logic means it's pure FPGA code. To gain the maximum flexibility it would be wise to let the communication do a CPU included in the FPGA. So on the way back to Kiel I investigated a bit how to do that and what should I use? In the end I decided to use a 6502 CPU. I found an implementation for Spartan 3 which can run at 100mhz. Niceness... 6502 is perfect for me since I already coded alot stuff on it... Also it would increase the productivity since I can code the bus communication in 6502 code. This is alot more flexible and implementation time is alot faster. I mean changing the FPGA code means about 2 or 3 minutes to wait until the FPGA code is implemented in a file with which I can programm the FPGA. But changing to a CPU for the commuication is quite a bit of work. it's a bit like ripping out the heart and replacing it with another one... Up next is to create the PCB for the bus interface... I'll do tomorrow let's see if I can handle this. The traces and spaces for the PCB are a bit beyond my possibilities here at home... Pushing the limits ;) Don't want to want 10 days to get manufactured PCB...Stay tuned And last but not least in my vacation a mail from my web hoster arrived. They said my webpage www.ultrafex.de have been hacked and they placed some stuff inside the sub directories. They are right. Indeed. Hm dunno how they did that I'm not using any wordpress/drupal/mysql stuff on my www.ultrafex.de page. It's just a link page. Also my FTP password is strong. Odd... |

| 18.05.2023 ultraDev+ STE |

Last days have been a bit stressy... Well tomorrow my vacation starts and going to Freiburg in Germany. I was working a bit on my house

(solar system at the roof) and work took quite some time. But I had some time to continue the tests for the new ultraDev+ hardware. The improved VGA stuff and ram is working. So basically everything works as planned. The thing I struggled the most was getting the ram to work. My milestone before my vacation was I want to write from the 68k directly to the new memory on FPGA in full speed. That works now ... hurray. But the way to it was a real nightmare. I had so many problems to get this to work like I connected the extended bus interface to the wrong places in STE, in my FPGA project uds and lds was exchanged, bad soldering point and mh the most time I struggled with the STE bus timing. Well too much self-confidence is not good. I mean well no problem I know how the 68000 bus interface works DTack UDS LDS kids stuff ;) But it wasn't. Basically it's no problem when you read how the bus interface works. I thought it's working like a normal static ram interface. Of course its not working like this. Reading the 68000 Users Manual could have saved some time ;) aaaaanyway The result counts. I'm now able to write directly to the FPGA memory in full speed. It's kind of mirrowing part of the STE memory to the FPGA memory. Ok not perfect yet only byte accesses are working but that's already most of the deal... So better stop talking I still have to pack my suitcase...cya |

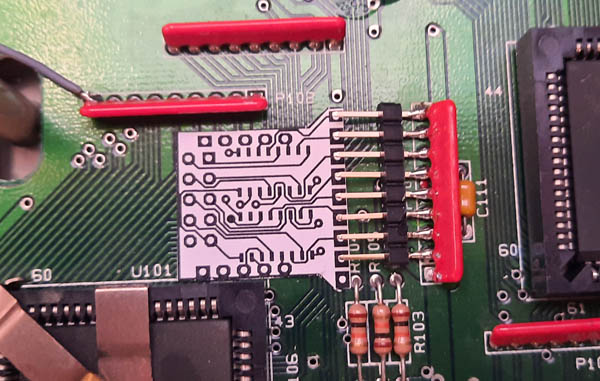

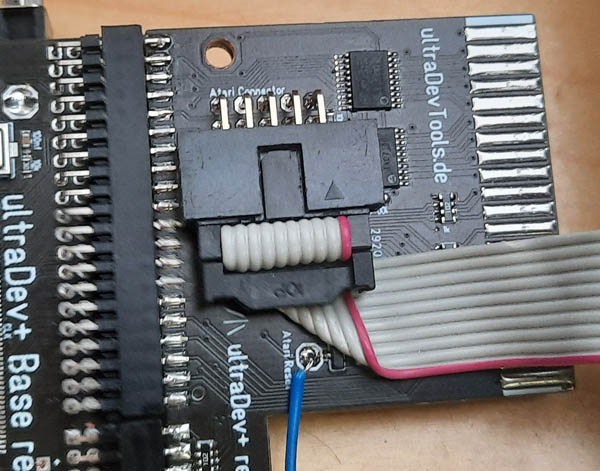

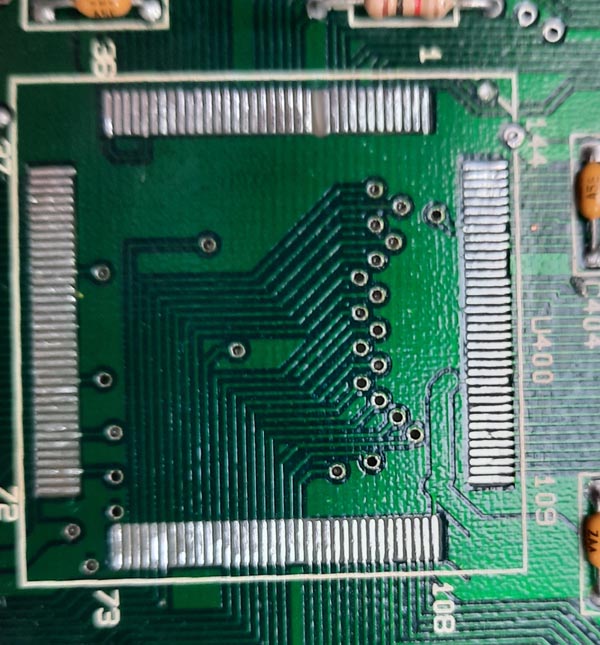

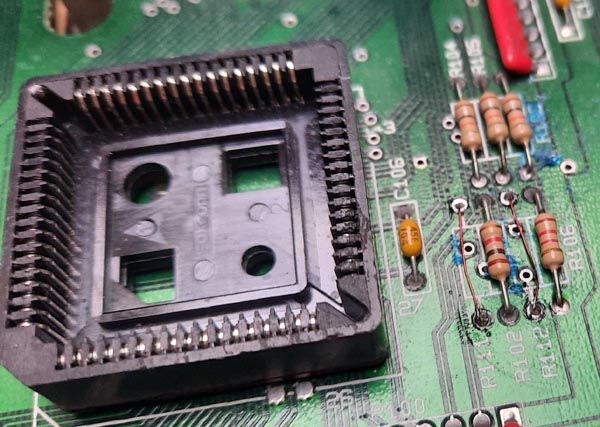

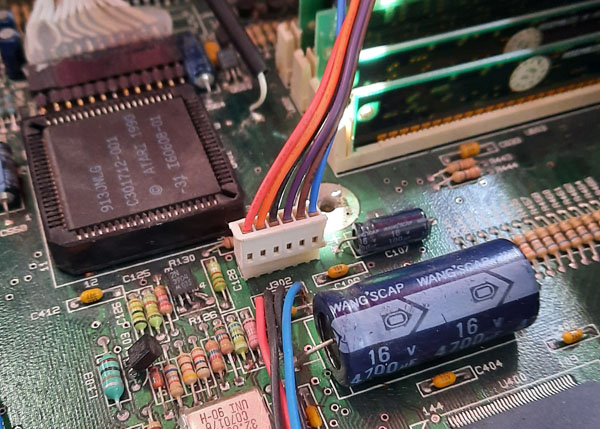

| 09.05.2023 ultraDev+ STE |

Today a tested a new hardware feature of ultraDev+ which is currently for STE only. I'm talking about the extended bus Interface. This is how it looks like:  As you can see not too hard to install... The new Atari cartridge connector has an additional connector to grab more internal signals. When you plug in the cartridge you also plug the small connector to the PCB. Of course this is not always needed only for some special features:  The connector holds the address lines from a16-a23, rw and reset line. Clock signal is not included. I have to do some tests to see if the clock signal can be grabbed without problems. But seems to work so far. I was able to let one of the leds blink on the cartridge by writing something to the $FF8240 register. This is pretty awesome... Next is to test the ram and its interface... |

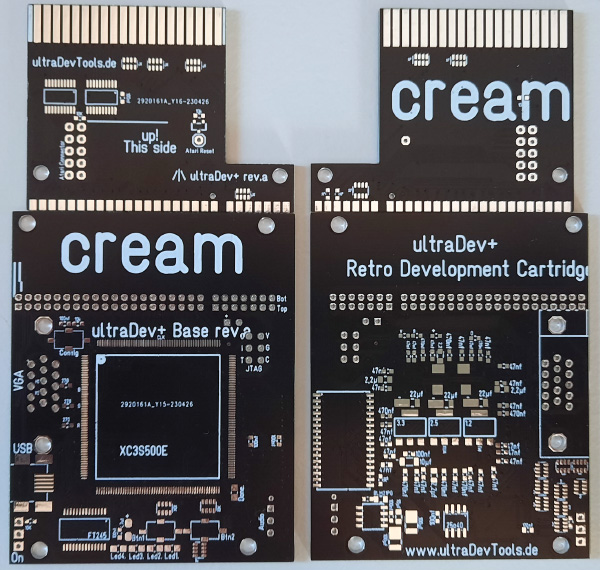

| 08.05.2023 ultraDev+ PCB |

Oh man. On friday I've got a mail from DHL your package will be delivered today. I thought yay this can be only my ultraDev+ PCBs !... Rest of the day I tracked the tracker by updating it every 5 minutes or so. ;) I want these PCB now! Shortly after lunch time suddenly the tracking disappeared just 2 stops before my house. Nothing happened for the next 4 hours. In the end it seems something happened during the tour and it was shifted to the next day. This was really mean. On the next day I finally got my package. This was included:  If you look closer you will see the first bug. The text is too long (cartridge the e is missing) oh noes... anywaaay...  Finally the new PCBs arrived. But I have to say this was quite fast I mean I ordered the PCB on 25.05 and they have been in my home town on 05.05. Not bad. And schnipp:  First fully build up ultraDev+ cartridge. As you can see the connector to the Atari ST can be changed. This means it is possible to create connectors for other systems. Or for example would be possible to create different connectors for Atari. One maybe for development, one with a sd-card holder to create something like Ultra Satan or maybe a floppy emulator. The strength of ultraDev+ is its flexibility... The new hardware features are quite powerful. I tried to look a little into the future and tried to develop the hardware with a view to the new features that might come. That was quite a bit exhausting, however, because developing hardware for something that doesn't exist yet or it's not yet clear what features might come. I changed the hardware several times and I mostly opted for the maximum solution. Interestingly I had a lot of new ideas for the Atari version of ultraDev+ during this time. It was exhausting but it was worth it I think. Build up itselt worked quite well. But the first build up needs always a bit more time. The PCBs looks quite alike the old version but there have been changed quite a bit. Also pins have changed. The first test of the cartridge of course did not work very well... That means tracing down bugs or mistakes. Well if you build up something for the first time you never know is it a problem of the hardware design, software/fpga code changes to make the new revision work or is it a problem because of a bad soldering joint? My goal was to have one firmware which works on the last revision f and the new ultraDev+. Luckily I was able to do this. I added some resistors to the PCB to identify if it is a ultraDev+ or not. State now is ultraDev+ works as good as the last rev. f which is quite good. So far now mega big hardware mistakes. The only shocking mistake was as soon as I connect a monitor the ultraDev+ and the Atari did not boot up anymore. Uff I already thought fuck did I blow up my Atari? After a checking the schematics again I unforunately saw I used the INIT_B pin from the FPGA during boot up it is not a good idea to pull this pin down. Connecting a VGA monitor did this. Workaround is just to connect a monitor after switch on anyway no big deal to change this. So up next is to test the new features of ultraDev+. I hope I'll not discover more heavy hardware bugs but until this point I'm quite happy it's working so far. Here again a compare ultraDev+ with rev.f:  |

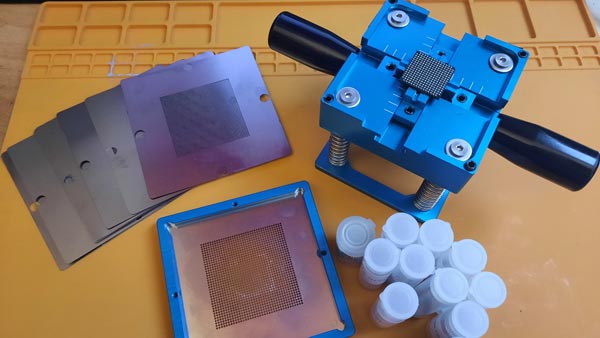

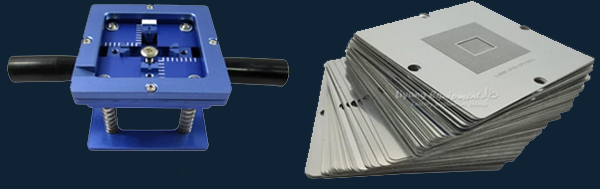

| 05.05.2023 ultraDev+ PCB |

Looks good so far. I have soon almost everything I need to build up the first ultraDev+ PCB. The PCBs are already nearby my home town. I guess I'll get them today... In the last days I was fighting a bit with cutting plotter to create my stencils. I use the stencils to print the solderpaste to the PCB. Hm do you know this? Everything worked fine last time. Next time you want to use it. It doesn't work. Meh. I have a cameo 2 cutting plotter to print out the stencils I use gerber2graphtech. A small too which can convert the PCB layout into cutting commands. Works not too bad. If it works. But the solution is a bit hacky like creating a link from the printer and then the tool outputs directly to this link. Unforunately the link I created 4 years ago changed its destination and it went from USB00x to LP1. Cool how can this happen? I mean I did not change this. Anyway that took quite a while to figure this out. I mean error while printing from Windows did not help here really. |

| 29.04.2023 ultraDev+ PCB ultraDev Fixes Interface Kiel |

Yay seems my PCBs for ultraDev+ are done and they have been already shipped... Cool. I have been working a bit on the prg-file start code on PC. I made it a bit more "intelligent" like recognising it's not a valid prg-file. It also handles can handle segments on odd adresses or stripping symbols from a file. I saw I always generate the Bugaboo prg-file with debug symbols.So each time you start the debugger round about 50 kb are transfered for nothing. Eh Ops ;) In future symbols are only transfered to the Atari when they needed. There is a small retro meeting today. Interface Kiel. Its not really a scene event but seems some scene ppl are comming over from oxyron or onslaught I'll check out never have been there if it is boring I'll go home and work on my stuff... Besides since I do not have a car (oging by bike) a good trip to get back my old fitness level ;) |

| 27.04.2023 ultraDev ultraDev+ PCB |

Seems all ppl who bought ultraDev are asm coders or not using the cartridge to code... I thought ultraDev can start everything until Matt came along with his small hello world prg ;) The file is generated by gcc vincent toolchain... which just don't work... Back in 2019 when I started the ultraDev project was not very into system coding (not that I am now anyway) one bigger thing I needed of course was to start a prg-file. Starting a prg file from disk or hd is no problem just use pexec. But how can I do it with an environment which can't load from disk or hd? Well no problem I thought... I have a relocation routine just load it and relocate and execute ... And done! ... Yeah... Hmmm not really and it turned into a real pain in the ass. I recognised more and more programms I can't start prg-files because they need the base page (something in for a process in Tos) so I started to build up a base page by my own. Hm unforunately it turned out in a real night mare... And of course with Matt's small hello world prg I had again a problem with the base page. I could fix that but it still not working fully. The file has debug symbols and seems gcc creates symbols with a odd length which results in a odd position for the relocation table -> address error ;) Ok fixed too Still don't work 100%... Bla. Oh man. And after 2 two years I think this was really a bad decision to create the base page by my own. But typical problem something which looks easy at the first glance mutated into something really complex. When do you pull the ripcord? Just a little more and then it works but this time really ;) Ok nice side effect is you learn alot. You get deeper into things but this need alot of time. Another problem I know of a PTerm of a prg results in a crash in ultraDev. Yeah no big problem normally but I really started to fix that problem by hitchhiking the trap and intercept PTerm to exit clean (but stopped that shorty after I started. unforunately some effects of my need for perfection...) You see my point? Just a little and it works ... really... ;) So today finally pulled ripcord and started to investigate how you can start a prg from ram legally with the system. I was browsing alot system sources and of course I read again the Tos reset handler and boot process. I did this in 2019 already which is the best point to execute the cartridge code. Luckily I found that position right before the execution of the auto folder... But why did I stop to read after that point? Well why didn't I read some more maybe 10-20 assembly lines more of the reset and boot process routine? Man that could have saved me days/weeks of work. What I'm talking about is when Tos is resetting it trys to boot from floppy/hd and what it does then? Yeah it enters the desktop. The desktop is started as a process excatly that what I need. Both things I needed that close to each other and I didn't find/see the second... That's life... Oki need to do an example how to start an incbin prg-file to see if this works and then change the entire prg-start code for ultraDev prg-files that will be fun. Wat mutt dat mutt... Like we say in north german jargon means "What has to be done, has to be done"... Something is almost done are my ultraDev+ PCB... They are surely done next week so maybe I can build up the first ultraDev+ before my vacation... That would be awesome... |

| 25.04.2023 ultraDev+ Atari 16bit |

The new PCB layouts for ultraDev+ are done and I gave them to the PCB manufacturer. Looks like this: As you can see the ultraDev+ PCB is slightly bigger than the last f revision. Mainly because of the connector and the new ram. On the lower connector to the Atari you can see the new connector for the additional adresslines. It's a 10 line cable can be soldered quite easily to the Atari. This is not needed for normal usage of the cartridge. This is more for future features I'm planning. Puh I'm happy the PCBs are done. Hopefully I included not too many bugs but we'll see in about mh 14 days or so. |

| 24.04.2023 ultraDev+ Atari 16bit Domain |

That idea with the second screen is huge but it makes only sense on STE. On normal ST I'll not try this. Some days ago I thought again how to speed up the screen transfer to FPGA memory (wrote earlier about that). Last idea was to sniff the bus and grab the reads from the movem (138 rasterlines that would need). Hmmm... Hmmm... I mean when I sniff the bus why should I transfer the entire screen to the FPGA? Why not grab the writes to the screen area? That would need no extra code and will be full speed. ... BOOM. What a cool idea! I could even create higher resolutions on the VGA screen. That is something I really have to try out. So in the last day I focused to finishing the FPGA base board and the Atari ST connector board. The ST connector I extended a bit and added the possibility to connect a small cable (10 lines). These lines are soldered to the STE to grab the rest of the address lines. To recognise the writes to a specific memory I need to clearly recognise the write addresses that works of course only with all address lines. The idea I had before with grabbing the reads from the movem would have worked with the cartridge ports address lines because I'm grabbing the data in a well defined time intervall. Writing to the screen memory can happen everytime so a 100% identification is inevitable. So the cable has A16-A23 (the ST full address range), 68k read/write signal. This Helps to sniff ;) Ah and also the reset line (no need to connect the reset cable anymore then). I think I'm almost done I hope I can send the layouts today or tomorrow to the PCB manufacuterer. I decided to shift the implementation of ultraDev+ for c64. I really have some more ideas for the Atari st version I want to try out first... And last but not least the page has now its own domain www.ultradevtools.de ... hurray;) |

| 14.04.2023 ultraDev STE |

Hm there was a sentence in my post yesterday which has kept me thinking the entire day. "Mh would it be possible to add a second screen to Atari ST? I mean a second screen on desktop?" I asked ggn if it would be possible to extend the Atari desktop screen to a second screen. And he said yes there is a tool which resizes the desktop and scrolls the screen or so (did not try yet). Maybe again what is the idea? The idea is ultraDev has a VGA output normally this is used for debug output but why not display extend the atari desktop to it? So I would need 32000 bytes on FPGA to have a output buffer. 32kb I have for 68k Firmware and HD sector buffer. If having a second screen output running it would not be possible to have HD emulation (mh or maybe only with smaller HD sectors currently they are 8kb). And the 68k firmware would not work or maybe only a smaller one. Hm that would work. But how to transfer the second screen to the FPGA memory? That could be a bit slow... The problem is that you can't write to the cartridge port. To write you can a) not set the address where to write directly and b) you are not writing you are reading from a specific address. Small example: lea $fb0000,a0 lea screencontent,a1 move (a1)+,d0 move.b (a0,d0),d0 this writes one word to the FPGA. Each write would need 24 cycles. That will be pretty slow... 160*200/2=16000*24 cycles/512 cylces per rasterline= 750 rasterlines (2,4vbl) heh ok slow... even if you optimise a bit like; move.l #$fb0000,d0 lea screencontent,a1 move (a1)+,d0 move.l d0,a0 move.b (a0),d0 160*200/2=16000*20 cycles/512 cylces per rasterline= 625 rasterlines(a bit over 2 vbl) mh slow... I almost skipped it because of the slowness... But wait a minute sometimes you need to go strange ways esp. when you have a FPGA in background which can do things which wouldn't be possible. I mean I have the 16 bit databus and 128kb address range available to the FPGA What if I do something like this: lea screenContent,a0 bsr setTheFPGAInASpecialMode movem.l (a0)+,d0-d7/a1-a6 /../ bsr disableSpecialMode The special mode activates some kind of address and databus tracing means each read access from the 68k is scanned and automatically written to the FPGA memory. movem.l (a0)+,d0-d7/a1-a6 needs 124 cycles if I'm right and moves 56 bytes. means 160*200/56 = ~572 movems to transfer the screen. 572*124/512 = 138 rasterlines. Maybe it would be possible to do it with the blitter... Yeah sounds like fun have to add this to my idea list... |

| 13.04.2023 ultraDev+ |

Puh finally the new FPGA board for ultraDev is routed. There is one word which descripes this task pretty good...

Annoying... Well the FPGA has 208 pins. To get the FPGA alive you need to feed 44 pins with 3 different power rails(3,3v, 2,5v and 1,2v) and 20 gnd pins. This is a challenge with a 2 layer PCB. Ok luckily I did not have to change this but this already limits the routing for the other signals... To handle this I had to change again track size and distance (0,15mm) again which means I had to rerout and shift alot of tracks... Vias are now 0,5mm diameter with 0,3mm hole. Pretty impressive that they can produce this without problems.. I'm still not at the limits of the PCB manufactor but pretty close... But pretty cool is that I could add ram without any problems. Means I have now 128kb ram with 8 bit size on the board. And the ram is pretty "fast" with 10ns. That's nice so it would be possible to create 128kb ram cartridges for Atari or for example a 640*200 display output on the VGA debug screen (true color.. hehe ok if you want to call 8 colors true color ;) ). Mh would it be possible to add a second screen to Atari ST? I mean a second screen on desktop... Mh2 maybe I really need to improve the VGA output to 256 colors... Hm I think I should add. Usually I choose the max. variation. That's the advantage of software development. Even if your initial design of a software was bad you can change it. If the design of the hardware is bad you a) Can not change it easily. Or better you can but this costs money b) it makes hardware updates and new revisions harder if you want to support the old hardware with the same FPGA core. So better to take yoru time if you aren't used in creating hardware stuff... But now the most annoying part starts. Checking the PCB... Man... This is so annoying... I really hate it. But it's really needed. Well so very easy forget one track let's say a power rail to a ic. Meh. But when it's done the most exciting part starts. Does everything works as you planned? It's so much fun when the first things are getting to work... And if you peek out new features with the current hardware which you initially didn't not plan or you didn't thought of... So... eyes shut and go for it... it's soon done ;) Hm almost soon done. Have to check the c64 connector again before I produce the PCB... But anyway not thinking about that yet ;) |

| 11.04.2023 ultraDev+ c64 version Ai |

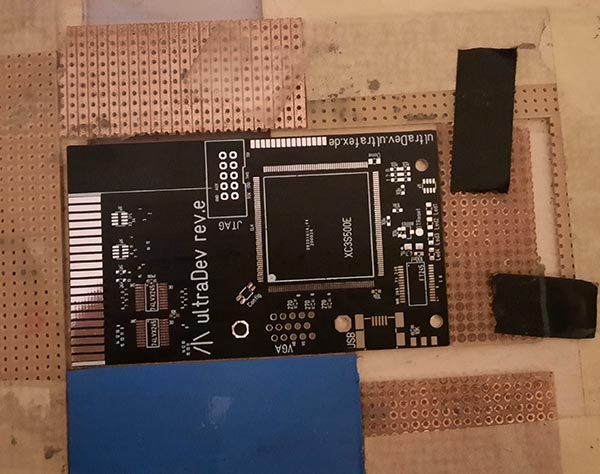

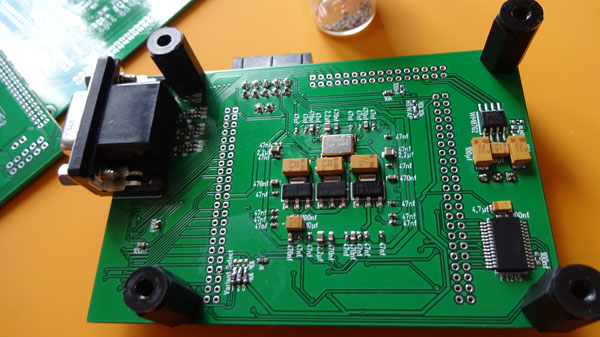

First of all some good news. ultraDev will be available soon again and there will be even a price drop. I could order some parts a bit cheaper... Back from 2 weeks of vacations (Hamburg and Föhr (a small german island)). That have been really relaxing... So time to continue a bit... Before my vacation I started to logic analyse the c64 bus.  Yeah looks a bit chaotic anyway ;) I could use the PCB with the scratch I created earlier to have a connector to the C64 cartridge port. As logic analyzer I use the the DSLogic Plus:  I like that one. it has max. 16 Channels and up to 400mhz sampling (in that speed you only can sample eh I think 4 lines). it supports RLE compression is improoves the max. capture time which is really cool it also can analyse standard protocols. The software is oki so far I read it is a fork of sigrok. it's not too bad somehow it fills my needs. When I bought it it costs about 110€ now it's 133 or so on Ali. I would recommend to buy the plus version instead of the basic. The basic has less memory and can not sample @400mhz. So far I read the 6510 can accesses the memory on the second half of the main clock. One thing surprised me during a write to the memory the write signal goes alot earlier to low than I expected means. Strange is that the time when it goes low also does not fit to the datasheet. Hm anyway have to check that again. I stopped the investigations for a while. Finally the new buttons for the ultraDev+ FPGA board arrived so I can finally finish the new FPGA board. Unforunately that took alot longer than expected and it's still not finished yet. Current state:  Not fully routed yet. As you can see (maybe) it looks a bit different from the old one. At the top I added some connectors so it can have a flexible bus interface to the destination plattform. The holes at the top are to fasten the bus interface pcb with screws. The new bus interface connector has more possible pins which would make it possible to have a floppy emulator for Atari ST by default on board. I'm talking about the HXC USB floppy emulator. Unforunately I can't find a floppy connector for a decent price. Bla this is really annoying... Really I don't know how long I searched the net also on AliExpress for this. Main changes are:

Maybe I should change to HDMi? Would be nice but after checking my ultraBooST PCB design again. HDMi needs by far too much iO ports on the FPGA. Also creating a HDMi output is not trivial. So I'll not change to HDMi. Also thinking about to add more colors to the VGA output. Hm not sure about that. Currenly I will stay on 8 colors. I mean it's a debug output. But you never know I change the decision if I add sram to the new version quite alot. The dac and sram will not be soldered by default. Currently I have no need for it this is just for future features. 2 weeks ago I decided to start a bit with Ai stuff. Means not only use it also how to code neuronal nets and how to train them. Just beause I have a problem at work which could be maybe solved better with Ai also I wanted to know how all these new and fancy features are done like image recognition. I know ChatGPT is out now for quite some time even GPT 4.0. But somehow I really started to use it last week. TBH I always ignored the Ai stuff because I had the feeling it will take some time till it will be useable. I mean look at the google assistent. Well ;) But I was really impressed by how "good" it recognises the speech. To get a bit more into the work Ai problem and develop possible solutions for the problem I started to read how neuronal networks are made and how machine learning is working. Really interesting stuff. Then I had the idea mh everyone is talking about ChatGPT why not talk to it about neuronal networks and how to programm and train them? Does ChatGPT understand my question? is it able to tell me how it works and does it understand my detailed questions? I had the last days quite a few chats over hours with ChatGPT about neuronal networks. And I have to say I'm deeply impressed by the chats of ChatGPT (even from the 3.5 version. 4 I did not try alot). This is really an interesting way of learning something new. I often don't know someone who could explain my questions. So the solution was always a) read a book and maybe your questions is not answered or b) you use google. I don't know how many hours I spent in google to figure out an answer to one question. Sure ChatGPT can't answer all questions. Also you have to be careful quite often the answers are incorrect or are true lies. I mean ask ChatGPT "do you know cream on atari" the answer does have some correct stuff but quite alot is not correct. Bing chat is more accurate but does not talk too much. Maybe it leaves out the stuff which is not correct... Anyway... Still this is absolutly awesome... Mh we are on the verge of a revolution in terms of Ai? I think that will change a lot in the next years. Even if I'm deeply impressed by what Ai is able to do not only chatgpt also midjourney (the ultraBooST title picture is done with it). I also have serious concerns. I think it could be some kind of pandora's box maybe a technical singularity? Heh ok maybe too dramatic ;) But it will cost alot of ppl's job also possibilities for crime is amazing. Mh also I think we need some more rules for Ai. Anyway so better to get into Ai as soons as possible and use the new possibilities. Ai will rise the level of productivity/creativity also for products how to make them smarter. |

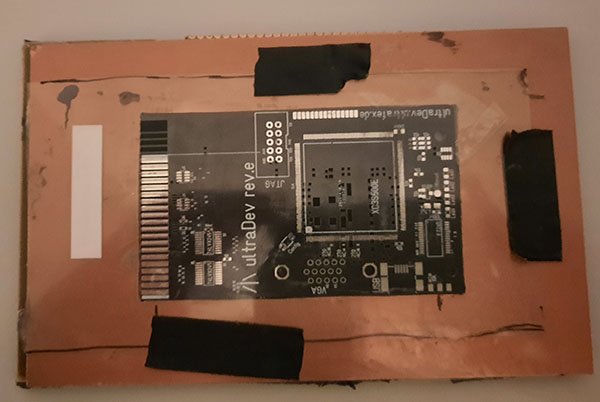

| 20.03.2023 ultraDev+ |

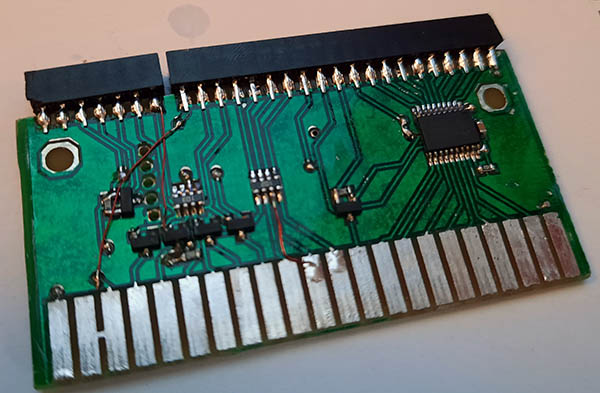

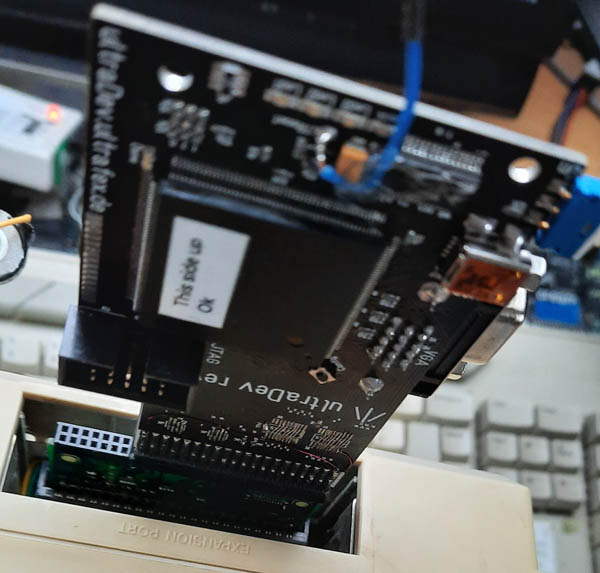

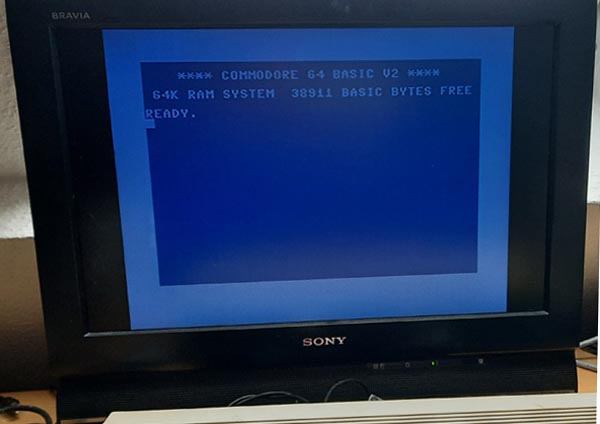

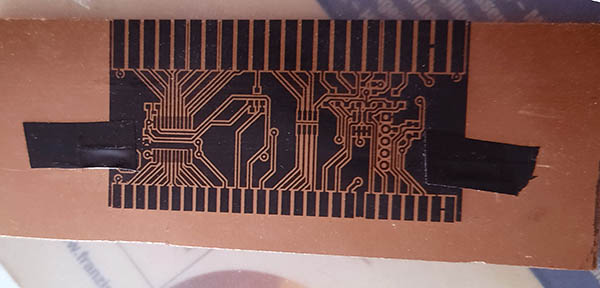

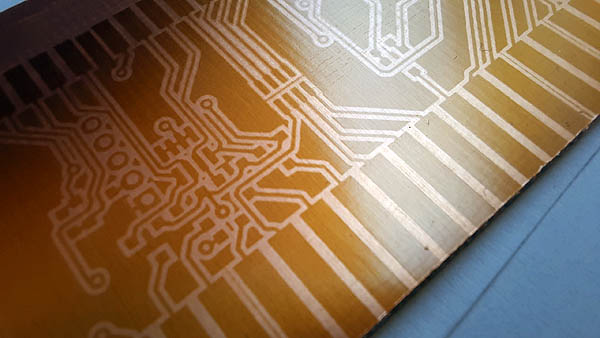

Continued in the last days to build up the c64 ultraDev+ prototype. Ah well  it's very nice if you etched the PCB and then you see there is a scratch over half of the PCB. Cool. That motivates! Anyway so I redid the PCB with the long scratch it makes no sense to continue. Unforunately the acid is in that a bad state that it took about an hour to each the PCB at 45�C.  That's the finished build up of the c64 connector prototype. No beauty I know ;) Hopefully it will work fine. The cartridge fits good in the cartridge port. Needs some testing before I connect to the c64. I mean it's the first version so better be careful;) The first version of ultraDev I just forgot the level converters and well 5v on a 3,3v accepting ic is no good... The FPGA commited suicide after that ;) (schnipp ...next day)  Currently there is no ultraDev+ FPGA PCB available so I had to modify an old one. As you can see (or not) I removed the entire Atari ST interface. The big connector is basically the ST cartridge port that smaller connector on the right has some extra lines and a 4 bit identifier. The 4 bit identifier is to identify the connector type. Each plattform will have its own FPGA firmware. What happens if for example if the FPGA is programmed to use an Atari ST and you change the connector to use it on c64? That could cause in the worst case a hardware malfunction. As soon as the 4 bit identifier does not fit to the programmed FPGA firmware the FPGA goes into a sleep mode. And all connections to the cartridge port are in a tristate. When you execute ultraDev on the host computer it checks the 4 bit identifier and programms automatically the correct firmware if they are different.  After I checked a bit the prototype. Now I dared to switch on the c64 for the first time (of course FPGA is empty)... And naaa? The c64 starts nicely. So at least I'm not fucking up the c64 bus ;) Next check can I access the FPGA? Yeah I can... Basically I'm ready to start the cartridge. So next will be to setup the FPGA project and implement the bus interface. But... tomorrow I'm going to Hamburg for some days... yay... |

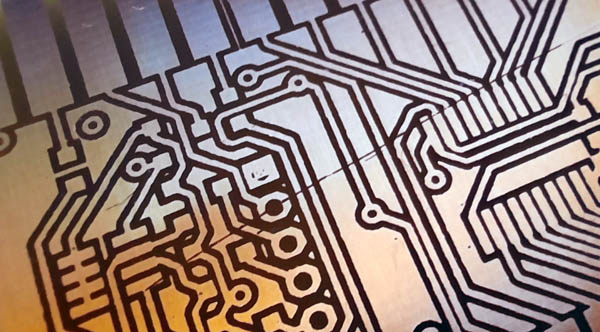

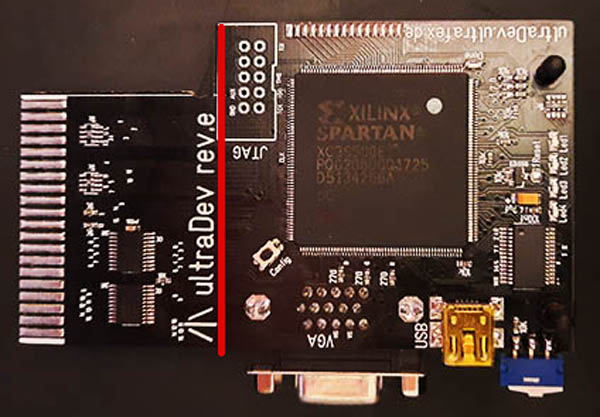

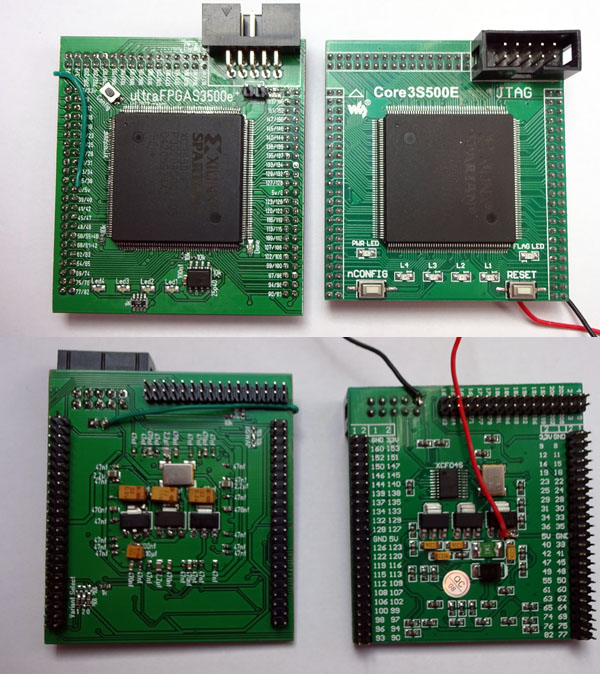

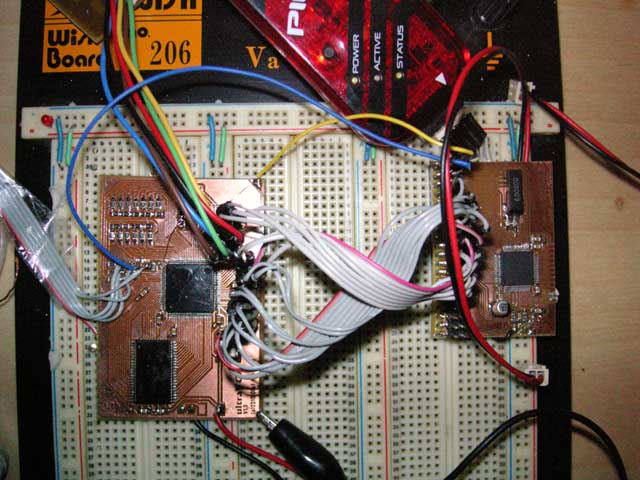

| 15.03.2023 ultraDev+ |

Some weeks ago I sent out the last ultraDev from the last batch. The last batch went pretty well. Except of the Ali Express trouble I mentioned below. Seems I woke up from my deep winter sleep and since some weeks I'm doing stuff on ultraDev again. Can you believe that? ;) Round about 7 monthes I didn't do anything neither ultraDev (except of buildup of course) nor Atari related stuff. But that long break was good. Time to relax, read maybe a book, just do nothing, meet friends, collect ideas and start with sports (lost 13kg of weight). interesting is what made me doing things again... 3 weeks ago I heard/watched a really cool podcast on youtube: "From typewriters to the VC-20: the early history of Commodore" (click) I think the title is self explaining. Unforunately it's german only. I really love these background stories and stuff just awesome. it's a 3 hours pod cast and dunno why this made my doing things again. Since ultraDev on Atari is working pretty good (so far I know ;) ) and mh tbh I don't know what to include next (tin your feature is still on my list;) I did not forget) I'm doing for me the next logical step. Currently I'm working on a multiplatform version ultraDev... so called ultraDev+... I think I talked earlier in the diary about that... My idea is to have one ultraDev base board. For each computer/console I plain to create a connector. You simply change the connector and you can work on other platforms with ultraDev. Out of my investiations/ideas I'm planning following Atari St (not too suprising;)), c64, vc20, c16 c116 plus/4, 2600 VCS, Lynx, Nes and Gameboy... if I really will support all these plattforms let's see ;) But of course I'm open for supporting other ones. So... destination next is?:  Huh? why a Commodore computer not Atari? Well the early Commodore computers have been my sweetheart. I never had an Atari 400/800. I only changed to Atari to ...do things together with the creamies... Hm but why c64? vc20 was my first computer? Well the c64 cartridge port is powerful. it offers more features compared to the vc20. Hm not to mention the Atari ST cartridge port. The c64 cartridge port opens up new worlds my feature list grow alot after I started to investigate the hardware... Just awesome... I know the c64 is pretty much saturated with stuff like 1541 ultimate or other stuff... But something like ultraDev is missing on c64. And tbh I'm not doing this to sell alot this will be a fun project. What I'm planning to do with ultraDev+ looks like this:  That's the current revision e of ultraDev. As you can see on the right side the FPGA board. On the left side you can see the Atari ST bus interface. The idea is to cut the ultraDev PCB at the red line and add some connectors. So the bus interface on the left can be changed. Another idea was to use the old ultraDev rev. e and the connector to other system has an Atari ST cartridge port. To find this connector is almost impossible. I don't know how many hours I spent on ali express to find such connector. I gave up. But it's I think good like this. I recognised using the Atari ST bus interface would limit the possibilities of new systems/consoles. I mean the Atari does not have a very strong cartridge port it's pretty weak. So having an especially designed bus interface for each system/console will peek the maximum out of each system. First step is of course to design the bus interace for the c64. Never had a closer look to the cartridge port of the c64 in the past. And have to say it's pretty strong one which opens up really nice features. This part of the design process of creating something new I really love alot. Understanding the cartridge port and see what you can do with it and in the end develop features ideas, think about what could be a problem, find a solution, what must the hardware be able to do and in the end layouting the hardware. For the c64 I've decided to support all lines mostly bidirectional. Sure that makes the bus interface more complex but I think it is worth. Looks like this (early stage):  And this time I'll try to do the prototype for the c64 PCB here at home. Yeah I didn't do that since mh 4 or 5 years. Well creating pcbs for the FPGA board at home is surely possible but unbelievable alot of work also the layout must be bigger... But the prototype for the c64 interface is no big problem... So up next is to create the PCB for it:  The layout for the PCB is exposed with an uv light. Of course the layout is double sided. Next is to develop the exposed PCB  The expose and develop worked pretty well for not doing it 4 or 5 years (sure depends also on the chemicals) the result is awesome... To have a good result here the most important thing is the film to expose PCB with uv light. The printed PCB layout must be opaque as good as possible. Of course you can do this with a laser printer. The upper picture with the layout film is done with a laser printer. No need for an inkjet printer that's nonsense. Use a plastic primer to make a laser printed layout opaque (I'm using Dupli-Color Basic plastic primer...Spay a little and dry it with a hair dryer and repeat 2-3 times). Without that step a printed layout is indeed unusable. With it works perfect I can do 0,15mm structures here at one... Up next is to etch the PCB. Let's see if the Natriumpersulfat (acid to etch the PCB) is good after 4-5 years... |

| 06.01.2023 Ali Express trouble |

Seems I have a run currently with bad stuff... First the Windows update which broke my Xilink iDE now I have trouble with a delivery of USB-Chips. Out of 10 ...3 are not the correct chips and 3 are not working maybe fakes. Really cool. So ultraDev delivery will be delayed... |

| 05.01.2023 FPGA ide trouble |

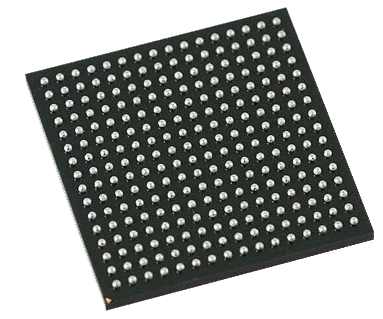

Some FPGAs arrived some days ago so I started to build up one ultraDev to see if the FPGAs are working fine. After finishing the soldering I wanted to programm the FPGA. But currently I'm not able to programm any FPGA because the ide (Xilinx ise Webpack) does not work anymore. Also making changes it not possible. Seems a Windows update made it not working anymore. So since yesterday I'm trying to reverse eng. with Ghidra and x64dbg man this is so annoying... Well the ide is already over 11 years old but it's the only verision which still supports the Spartan 3. Well I like the Xilinx FPGAs but their software is a real pain in the ass. Hm maybe I need to check if the VM solution for ise Webpack is an option. I planned to start to deliver in january new ultraDevs... anyway I guess I can forget that... |

| 12.12.2022 rl ultraDev |

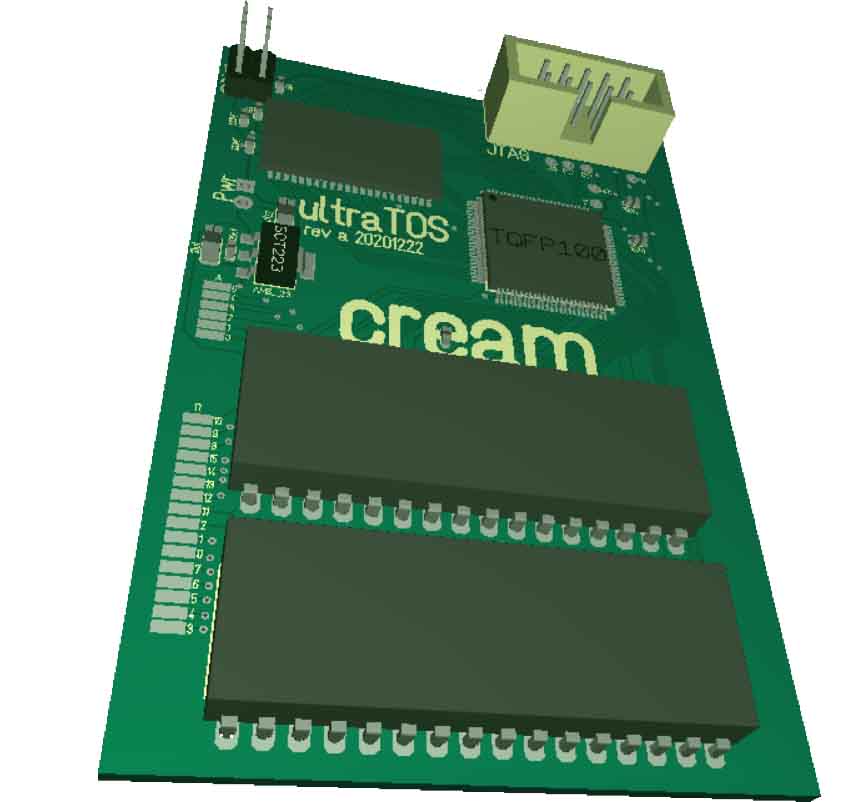

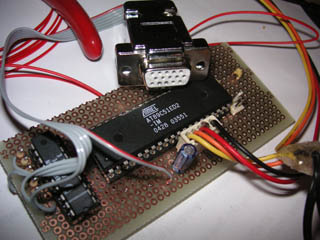

Not much happened tbh. here ;) I had a longer Atari break after my contribution for the Silly Venture 2022 summer edition. it ranked first in the wild competition. in case you missed it: it is a demo which was created with a video modification developed by me. if you scroll down you can see some of the PCB which I used for the video mod. if you want some more infos about the project you can get them here: Clicky. The ultraBooST project I was working about 3 1/2 years. And since you did not read something here it was a secret project. Everthing you see here like ultraDev and ultraTos was done to realize the ultraBooST project. I wanted to share infos the about the ultraBooST project when it's more or less done. The last 4 monthes I did not switch on my Atari at all... Well the 6 weeks before the party have been really stressy... Also it was really needed to do some improovements to my house like solar system on the roof and to improove the insulation of the house. Luckily I managed to get done before it's getting really cold... And it was worth insulation is not much but helps to keep the house warm. So what I'll work on in 2023? in 2023 I'll work a bit more on ultraDev I think. Currently I'm working on a new revision of it. The idea is to use ultraDev not only as a development system for Atari St/Falcon. My idea of ultraDev is to have one development hardware for the most common plattforms. That was the basic idea of ultraDev ok the basic idea was bound to Atari St computers since this is more or less done I'll start to implement other systems now. Means the connector to the Atari ST is replaced by a pin connector and then you can plugin connectors for the systems like Atari St, C64, VC20, C16, VCS and what ever is needed... The idea is to have one development system for the most common retro computers. For example for c64,vc20 and c16 it would be possible to create a floppy emulator. Of course would be possible to create a floppy emulator for Atari too but really hard to get these floppy connectors :/ I already did 11 years ago one with a pic32 a cycle excat floppy emulator for commodore systems:

On the right you can see the cartridge which was done for a VC20. On the left you can see a emulation of the floppy and a very basic emulation of a vc20. This was mainly used to get into commodore floppy loading and stuff. The floppy emulator hardware was based on a pic32 with cycle excat emulation of the floppy. Worked quite nice... Of course that would be some work to port that to FPGA but anyway. That's it for now... Ah and I almost forgot. in 2023 ultraDev will be available again. Only a few cartridges I can sell... Half of them are already sold tbh. But I'll devliver after new year 2023... leaving very soon to my traditional to Boltenhagen vacation before xmas . |

| 18.07.2022 ultraDev |

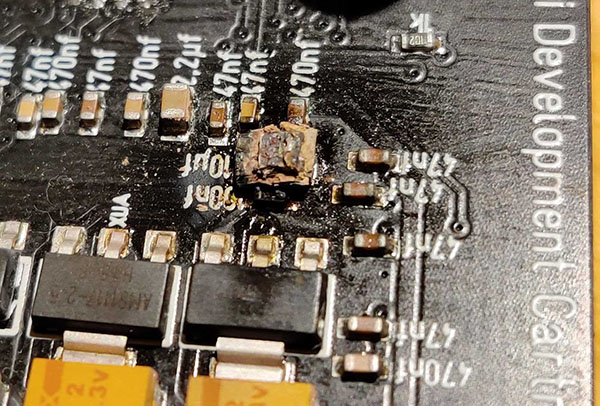

And now it happened... The first broken ultraDev device: The guy inserted the cartridge upside down. And switched on and wondered why it does not work. Hm so better double check before you insert!. I really hope I can repair it. I'll see if I can do something against it in the new revision. |

| 07.07.2022 Osc repair & mod |

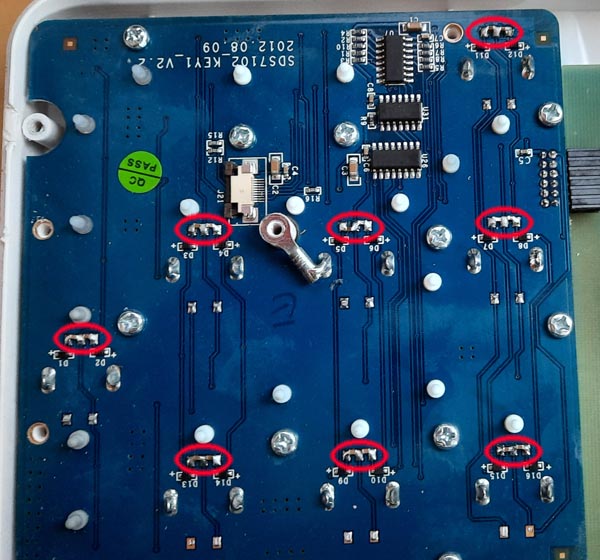

Today I was working on my sds7102v osc. Looks like this: Yes I was one of these morons who bought this oscilloscope. I think if I would have a top 10 of regrets buys this one would be close to #1. Well back in time this was ones cheap and worked so far. But after some weeks I could switch it on anymore. So I sent I back to the seller and it took about 2 monthes to repair. And well I never really liked the osc the rotary encoders do not have an accel which is a pain in the ass to scroll in a sampled area. Second thing which is really annoying is the fan. its so loud unbelievable. Do you know this you switch off something and you are thinking ahh finally silence ;) Some days ago I switched it on and now the rotary encoders are almost unuseable. Great!. Well it's a cheap china thing and often they save parts and try to solve problems with software. So my guess was the debouncing of the rotary encoders is done in software. That works for while but if you don't do it correctly the encoders will start to jump arround and in the end it's unusable. But this is normal for cheap encoders the bouncing increases after some time. So I opened up the osc today and checked if the debounce is done by hardware or software. And it seems it's done by software. The osc PCB with the rotary encoders from the back side:  The red circles mark the rotary encoders pins (3 pins for each). What I did now is just so solder two 0603 capacitors (100nf) to each encoder. That's surely not a perfect solution means not every roation speed will work. But it turns out it's working pretty well. Niceness ;) Next is to replace the fan. Replacing it is a bit annoying you have to get apart the entire osc. Fits perfectly:  I used MF60101V3-1000U-A99 from sunon for it. The fan is almost not hearable anymore... This is awesome. Hm the traditional left overs after a repair... But seems to work without ;)  |

| 01.05.2022 Xbox |

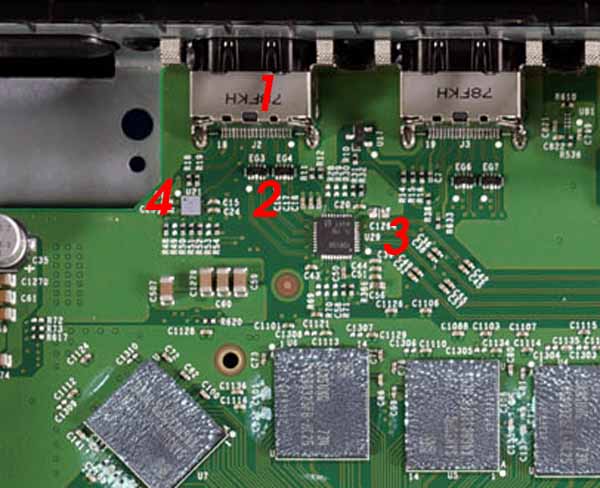

Last week I was browsing throu eBay and I found a faulty Xbox one X with no HDMi output. And something said me hm buy me ;) Tataaa... it arrived on friday. it switches on normally as you can see the Xbox-Logo lights up but does no display a picture on tv. Lets see if I can get it back to life.  On the upper picture you can see the HDMi circut of the Xbox one x. What can cause a no display on a Xbox one X and how to diagnose it? -A faulty HD. You can recognise that if you switch on the Xbox and if it switches off after 1-2 minutes... my Xbox -> it stayed on so no faulty HD. -On the upper picture 1) That's the HDMi port. inspection from the outside of the HDMi port looked oki. Next is to check if all pins are soldered correctly. Small nudge check on each pin... -> HDMi Port is in mint condition and all pins are soldered correctly. -On the upper picture 2) ESD diodes they protect the internal circut against over voltage. Switch multimeter to continuity mode and check the HDMi lines if there is a continuity for each lines. All is fine here. Next red probe to ground and check the lower HDMi lines of the ESD diodes. Multimeter should display 0,7... All fine here...-> ESD Diodes are fully working. -On the upper picture 3) Thats the retimer chip. it mainly does a level shift of the HDMi signals to TMDS it also can boost the HDMi signals and stuff. Switch multimeter to continuity mode and black probe to ground. Now check each capacitor around the iC of there is a short cut to ground. All is fine no short cut. Next check c50 in resistance mode of multimeter C50 should have around >8kohm. Fine... -> So retimer chip seems to be ok. -On the upper picture 4) ESD Booster iC chip. it does ESD protection for hot plug detect, i2c lines of edid and over voltage protection for 5v. Checking all capacitors around that iC for short cuts. All is fine. Next checking if hot plug detect and i2c lines are 5v when the console is switched on. All is fine. So seems that iC is oki... Hm that's odd all test were successfully nothing seems to be broken. Then I checked the circut again with magnifier glasses. All fine... Hm but the retimer iC (#4 on the pic) seems to be changed by someone. After inspection of all of pins I recognised not all pins have been soldered correctly. ... Oh So I fired up my soldering iron and resoldered the chip again. Switch on and???  After seeing the Xbox one X logo a loud shout out "YESS!!" came up... That's cool I didn' even have to change a chip to get it working that was a cheap repair... The next questions is why I'm buying a Xbox one x? I'm a playstation guy. The reason for that is that I know there is a problem with repairs of the Xbox one x and also on Xbox series x. The problem is on the upper picture #4 the ESD Booster iC chip. You can't buy this ic. if this is broken the Xbox is a brick and can't be repaired (except of Microsoft of course). There is a possibility of bypassing this chip but then you do not have a ESD protection anymore also you aren't able to display 4k anymore. So the idea is to do a replacement PCB for this chip. After reading the ESD booster datasheet for the Xbox one I know what the iC is doing so creating a replacement PCB isn't that hard. So next step is to desolder this iC and creating a replacement PCB for it. |

| 12.04.2022 ultraDev |

Two days ago I had a talk on irc in #atariscne and ppl were asking when there will be a Linux x64 support for ultraDev. Well I do not have a Linux machine. First idea was to create a USB stick to boot from. After some browsing on the Ubuntu page I found a WSL Ubuntu. WSL is Windows-Subsystem f�r Linux means you can install the WSL version of Ubuntu and after it you can execute native Linux stuff on Windows. A bit like Wine on Linux but just the other way around. I liked the idea and installed it immediately. Unforunately I had real problem to get this to run or better to get internet access to run. in the end it was the windows file compression which is activated on my hd. The problem here was the %temp% folder which was compressed too and ended in a network is unreachable in the WSL environment... meh. Anyway... after this was working fine gcc install and download the USB driver libs for my USB ic pling compile and after about 10 minutes I had a Linux x64 version of ultraDev. AWESOME ;) tin and Troed tested it a little and it seems to work fine. Double awesome... ;) Pretty nice is that I can create the Linux x64 version in my automatic build script which creates all binaries and finally a release with one click. Means next release will support Linux x64. I know quite a few ppl are waiting for it. |

| 01.04.2022 ultraDev |

Some bad news (no 1. of april joke). I'll stop producting ultraDev for a while now. More infos you can find on the preorder page (Click for the bad news) |

| 29.03.2022 ultraDev |

Started to sell ultraDev on eBay. if you saw and wondered why it costs 65 Euro (incl. shipping) well I added the eBay commission to the price. I was hoping the buyer would buy it over my page but hm didn't work. There of course I still offer the cartridge for the old price. The ultraDev was sold after some hours I'm happy. Talking about the prices... Unforunately I have to rise the prices for ultraDev soon. Chip shortage finally reached me too. The prices for the iCs rised quite a bit. For example the FPGA is now 35% more expensice. That's very sad. But I have some iCs left in my desk to build up some ultraDevs... not many but anyway. So if are thinking about to buy one you should do soon... Otherwise u'll have to pay the new price. How much it will be I have to see. Talking about build up... in the last days I build up two new ultraDev which I'll sell on eBay after my traditional tests... Even some code on ultraDev ok already some time ago. I started a new feature tin wanted to have. As you maybe know you can upload a new 68k firmware to the cartridge. But it is lost after the Atari is switched off. if you did changes to the firmware and it should stay resistant even after a switch off this will be the solution. Means the custom firmware stays in the SPi flash until you erase it or if you reflash the FPGA firmware. Changing the 68k firmware is not possible for normal users. The 68k firmware is included in the FPGA firmware and can't be changed. What I'm doing (or better will do) I check a special position in the SPi flash and if it has something except of the init value I load the SPi flash data to the 68 firmware space. Ah damn I really have to release the 0.57 of ultraDev finally since it has quite some new features. The 0.56 version is from 10.01.2021 over a year uhh. But well the 0.56 version is pretty stable... Someone said "never touch a running system ;)" |

| 09.02.2022 ultraDev |